EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 237

VIC_VEC_ADDRESS

0xFFFFF100

10.3.8 VIC_VEC_ADDRESS

Interrupt Vector Register

There are 32 VIC_VEC_ADDRESS registers. The address of each is calculated as VIC_VEC_ADDRESS(x) = 0xFFFFF100 +

(x*0x4). So, VIC_VEC_ADDRESS(0) is at address 0xFFFFF100, VIC_VEC_ADDRESS(1) is at address 0xFFFFF100 + 0x4

and so on. The definition of each of these is the same.

This registers holds the address of ISR for interrupts. 32 registers for 32 lines. There are 32 of these registers, which are con-

tiguous. Note the offset for this register bank.

31:0 ISR_ADD[31:0] The firmware accesses this register only after disabling the corresponding interrupt. Holds the

address to the ISR for interrupt number = the position of this register in the bank of 32 registers.

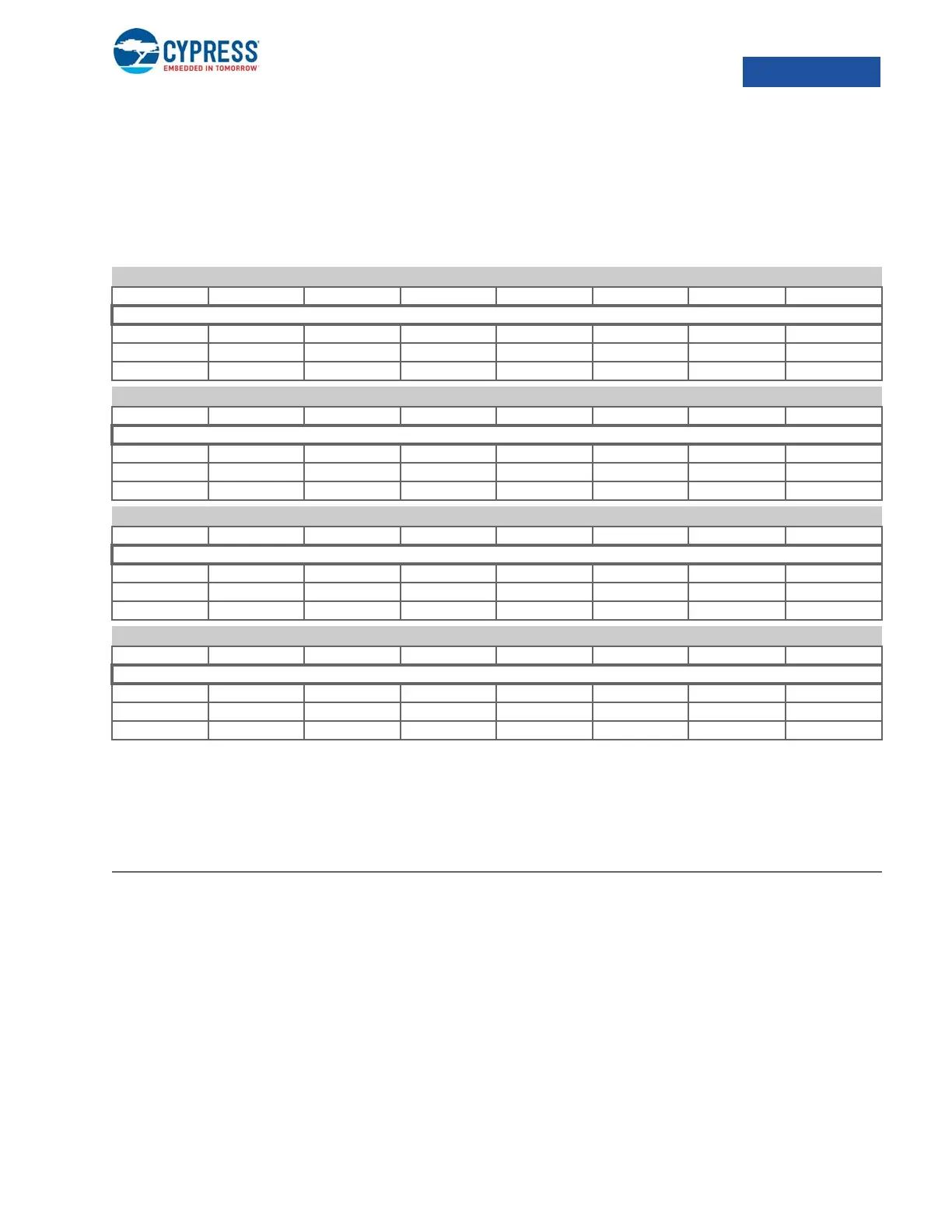

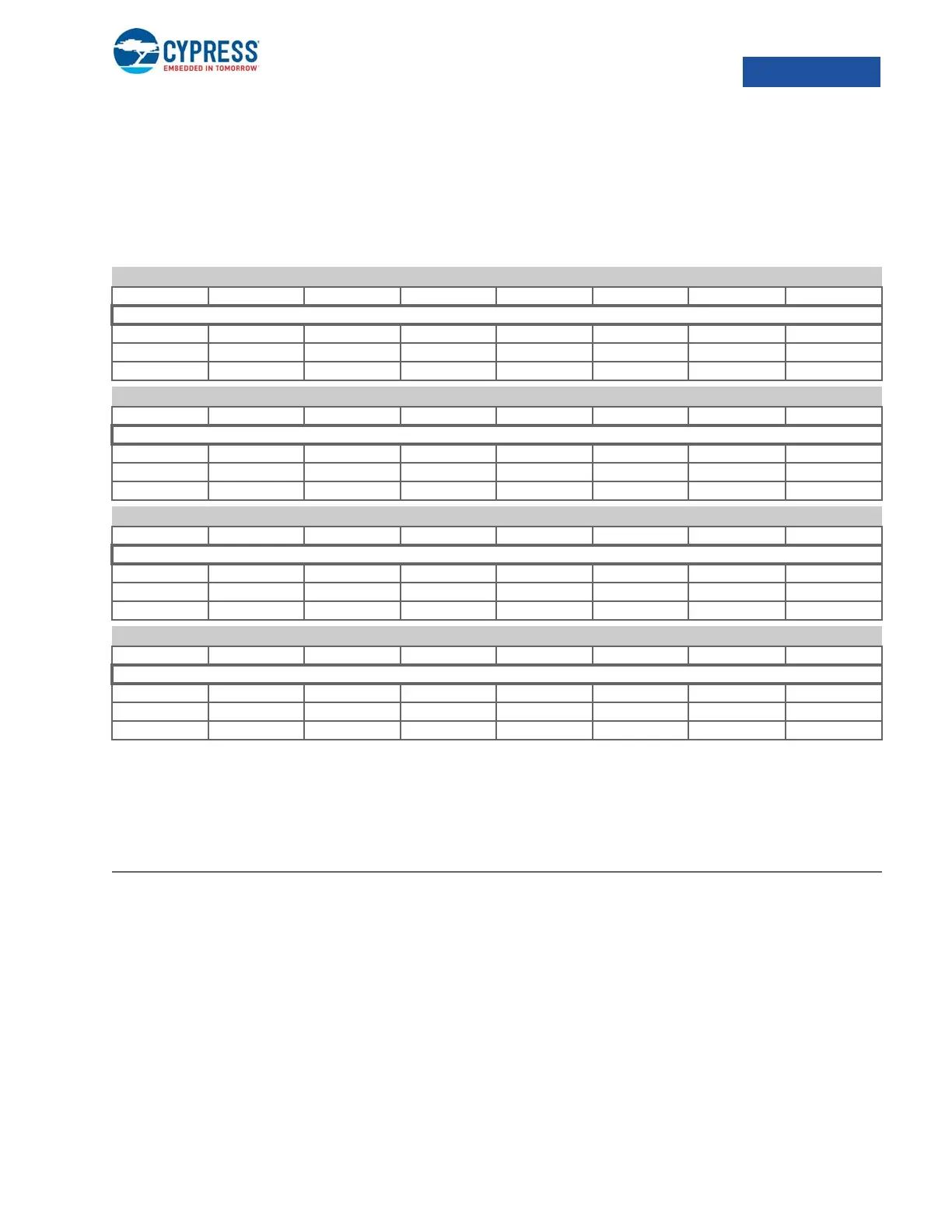

VIC_VEC_ADDRESS Interrupt Vector Register 0xFFFFF100

b31 b30 b29 b28 b27 b26 b25 b24

ISR_ADD[31:24]

R/W R/W R/W R/W R/W R/W R/W R/W

R R R R R R R R

0 0 0 0 0 0 0 0

VIC_VEC_ADDRESS Interrupt Vector Register

b23 b22 b21 b20 b19 b18 b17 b16

ISR_ADD[23:16]

R/W R/W R/W R/W R/W R/W R/W R/W

R R R R R R R R

0 0 0 0 0 0 0 0

VIC_VEC_ADDRESS Interrupt Vector Register

b15 b14 b13 b12 b11 b10 b9 b8

ISR_ADD[15:8]

R/W R/W R/W R/W R/W R/W R/W R/W

R R R R R R R R

0 0 0 0 0 0 0 0

VIC_VEC_ADDRESS Interrupt Vector Register

b7 b6 b5 b4 b3 b2 b1 b0

ISR_ADD[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

R R R R R R R R

0 0 0 0 0 0 0 0

Bit Name Description

Loading...

Loading...