EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 541

I2C_CONFIG

0xE0000400

10.19 I

2

C Registers

10.19.1 I2C_CONFIG

I

2

C Configuration and Mode Register

Various modes of the I

2

C block

31 ENABLE Enable block here, but only after all the configuration is set. Do not set this bit to 1 while changing any

other configuration value in this register. This bit will be synchronized to the core clock. Disabling

blocks resets all I

2

C controller state machine and stops all transfers at the end of current byte. When

DMA_MODE=1, data hanging in the transmit pipeline may be lost. Any unread data in the ingress

data register is lost.

30 TX_CLEAR Use only when ENABLE=0; behavior undefined when ENABLE=1

0 Do nothing

1 Clear transmit FIFO

(After TX_CLEAR is set, software must wait for TX_DONE before clearing it)

29 RX_CLEAR Use only when ENABLE=0; behavior undefined when ENABLE=1

0 Do nothing

1 Clear receive FIFO

(Software must wait for RX_DATA=0 before clearing this bit again)

continued on next page

I2C_CONFIG I

2

C Configuration and Mode Register 0xE0000400

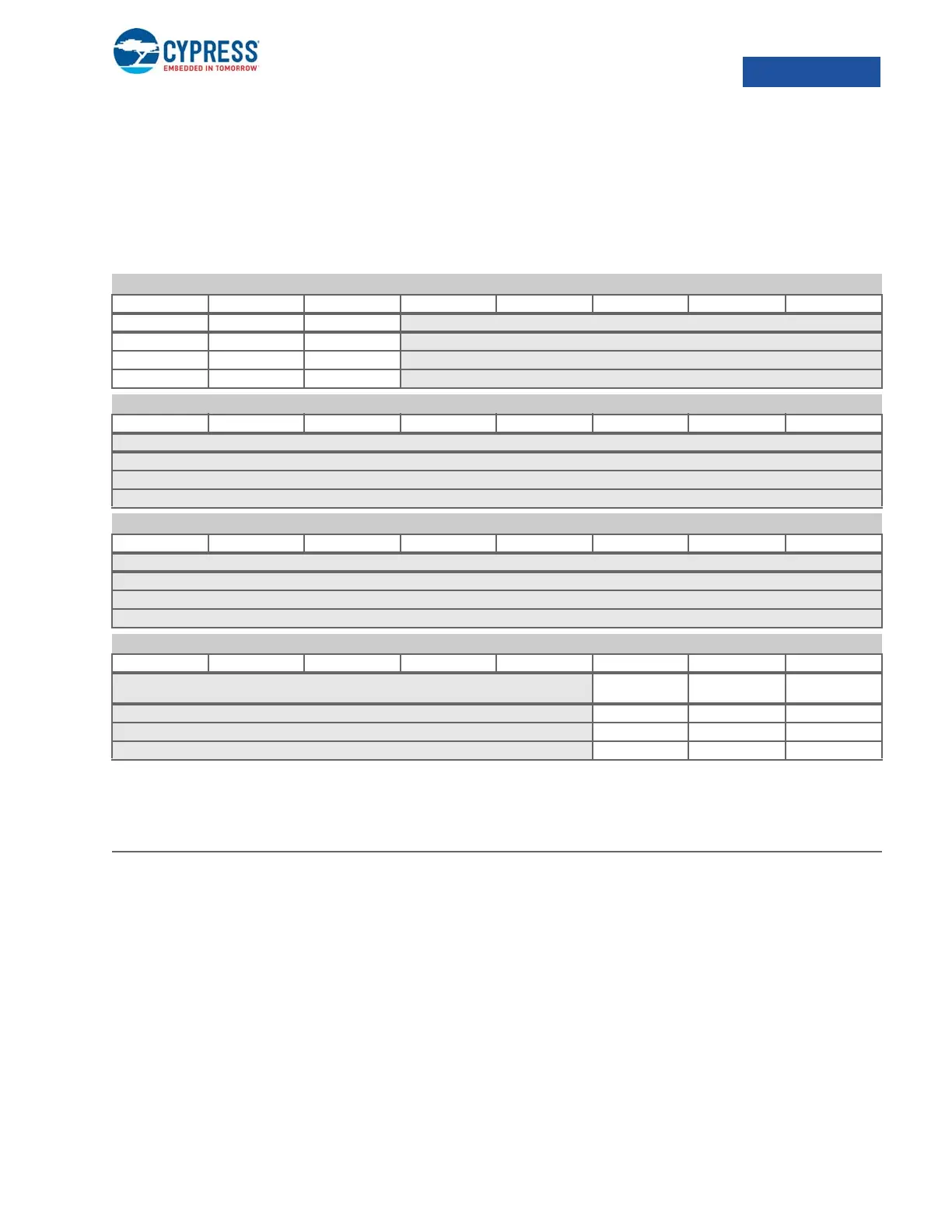

b31 b30 b29 b28 b27 b26 b25 b24

ENABLE TX_CLEAR RX_CLEAR

R/W R/W R/W

RRR

000

I2C_CONFIG I

2

C Configuration and Mode Register

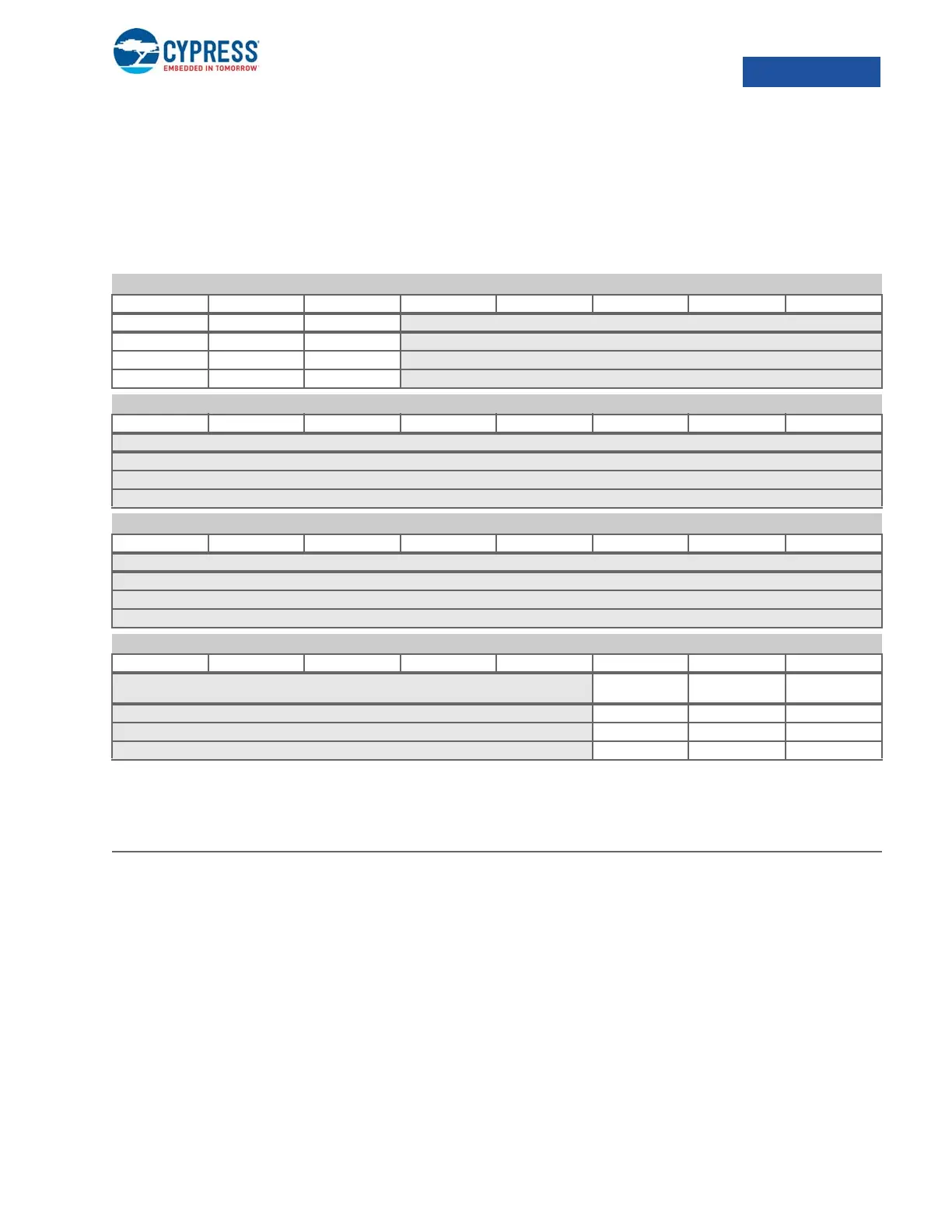

b23 b22 b21 b20 b19 b18 b17 b16

I2C_CONFIG I

2

C Configuration and Mode Register

b15 b14 b13 b12 b11 b10 b9 b8

I2C_CONFIG I

2

C Configuration and Mode Register

b7 b6 b5 b4 b3 b2 b1 b0

I2C_100KHz

CONTINUE_ON_

NACK

DMA_MODE

R/W R/W R/W

RRR

100

Bit Name Description

Loading...

Loading...