EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 605

SCK_DSCR

0x00

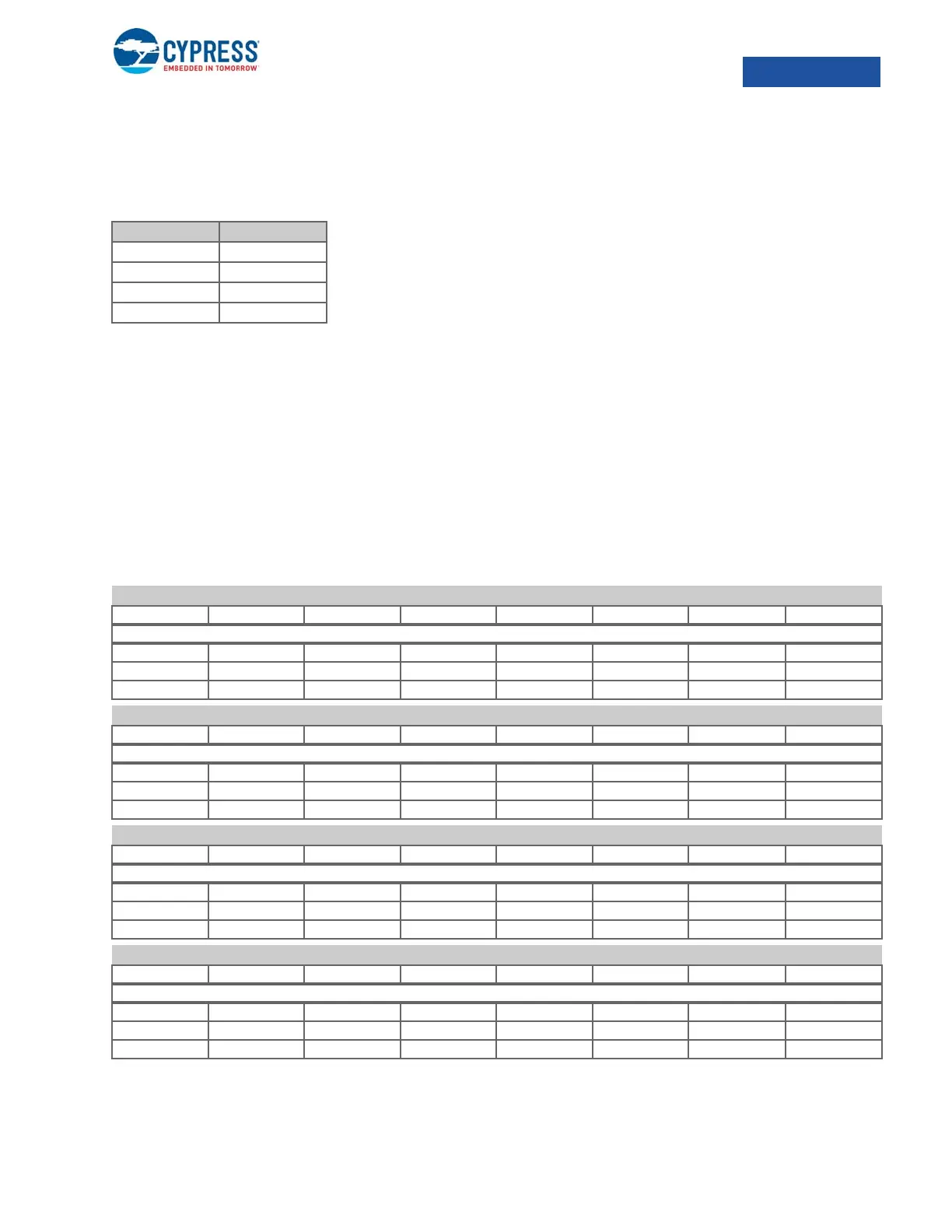

10.25 DMA Socket and Descriptor Registers

Each functional block (LPP, PIB, UIB, and UIBIN) has its own set of DMA socket registers that use the offset address of that

block. Table 10-3 shows the offset address for each block.

Each functional block has more than one DMA socket and each DMA socket has the same set of DMA Socket registers. The

offset of each DMA Socket register set is 0x80 (that is, the offset of DMA #0 is 0, DMA #1 is 0x80, DMA #2 is 0x100, and so

on). The address of a DMA Socket register can be calculated as:

functional block address + DMA # * 0x80 + register address

For example, the address of the DMA_STATUS register of DMA #2 in the UIB functional block can be calculated as:

0xE0038000 + 2 (DMA #2) * 80 + 0x0C = 0xE0038000 + 0x100 + 0x0C = 0xE003810C

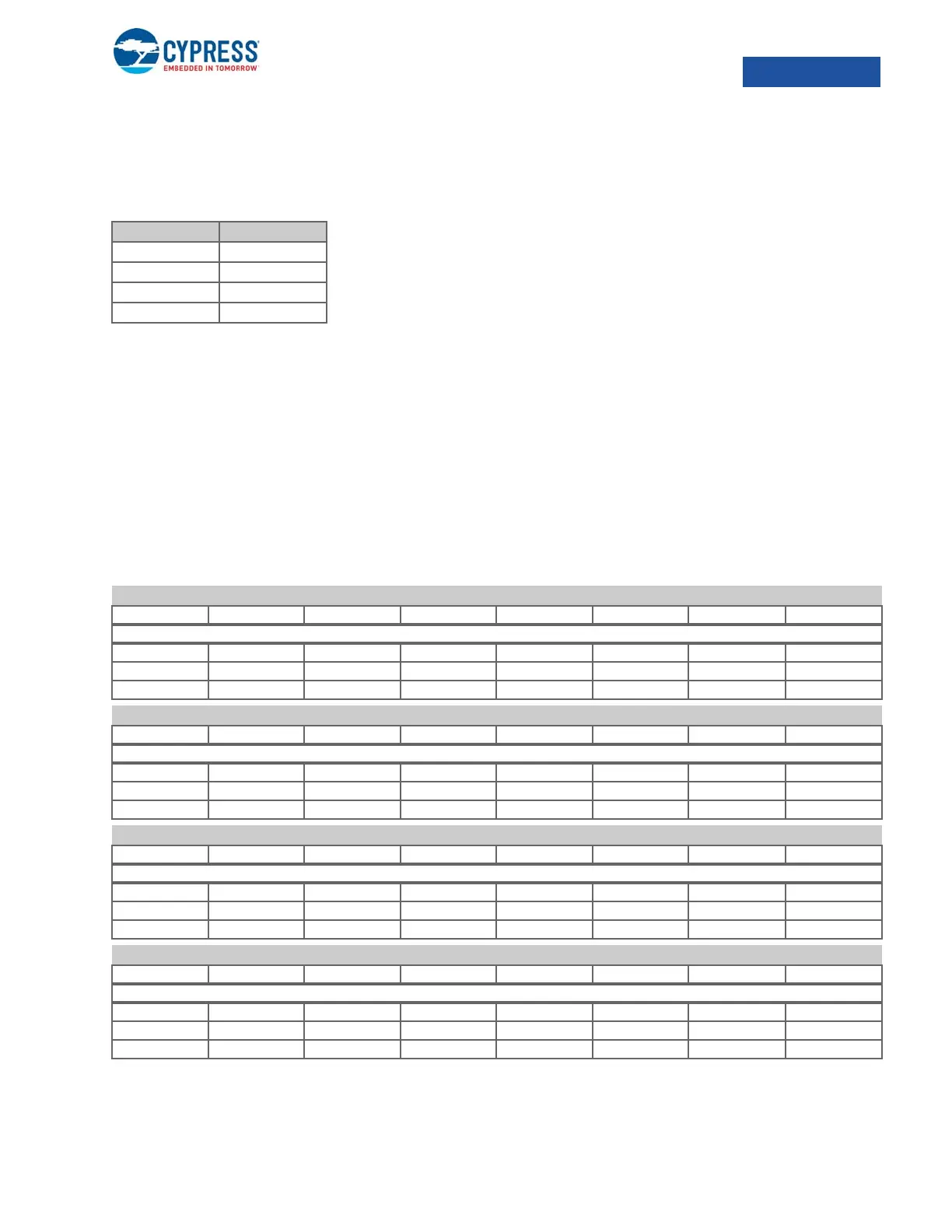

10.25.1 SCK_DSCR

Descriptor Chain Pointer Register

Table 10-3. Offset Addresses

Functional Block Offset Address

LPP 0xE0008000

PIB 0xE0018000

UIB 0xE0038000

UIBIN 0xE0048000

SCK_DSCR Descriptor Chain Pointer 0x00

b31 b30 b29 b28 b27 b26 b25 b24

DSCR_LOW[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

XXXXXXXX

SCK_DSCR Descriptor Chain Pointer

b23 b22 b21 b20 b19 b18 b17 b16

DSCR_COUNT[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

XXXXXXXX

SCK_DSCR Descriptor Chain Pointer

b15 b14 b13 b12 b11 b10 b9 b8

DSCR_NUMBER[15:8]

R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

XXXXXXXX

SCK_DSCR Descriptor Chain Pointer

b7 b6 b5 b4 b3 b2 b1 b0

DSCR_NUMBER[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

XXXXXXXX

Loading...

Loading...