EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 162

General Programmable Interface II (GPIF II)

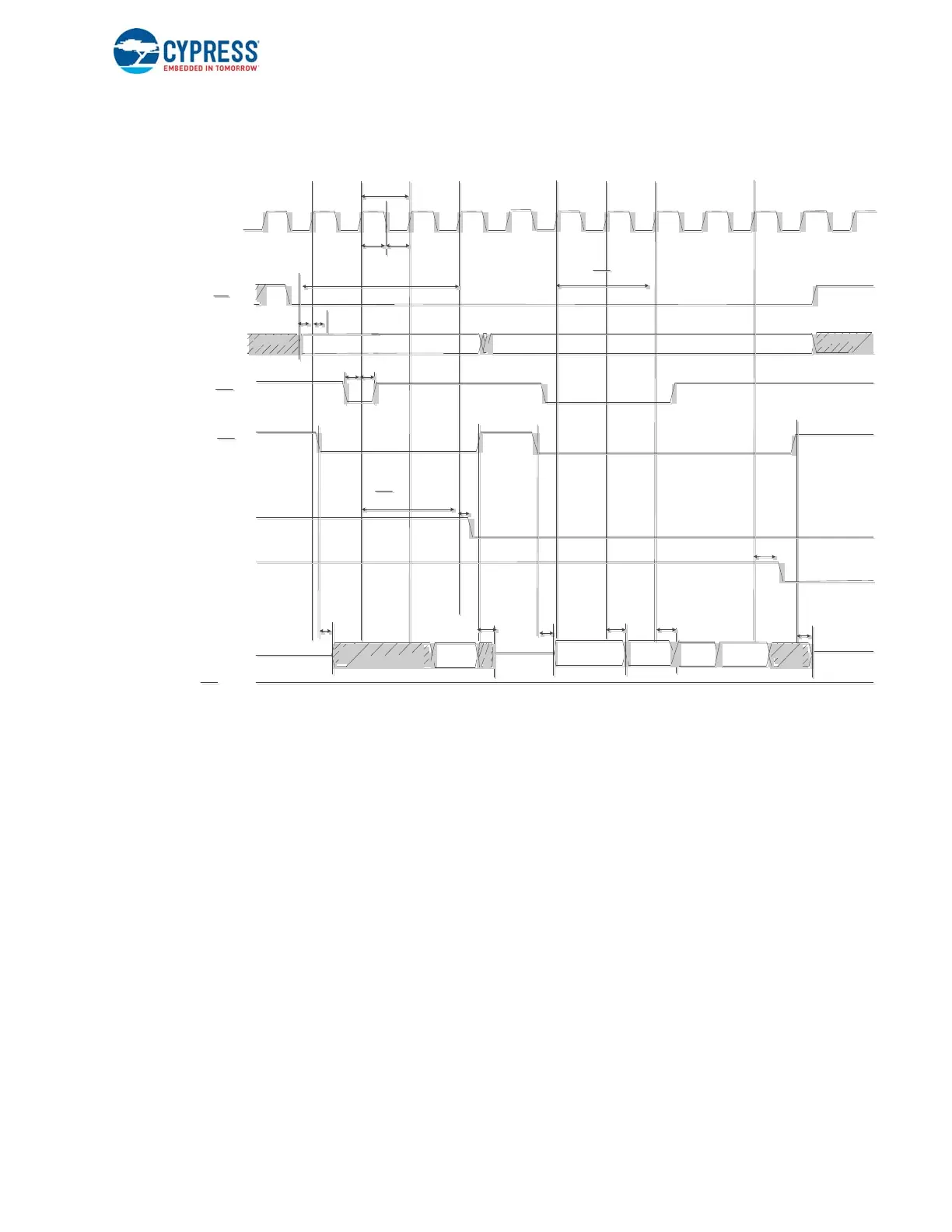

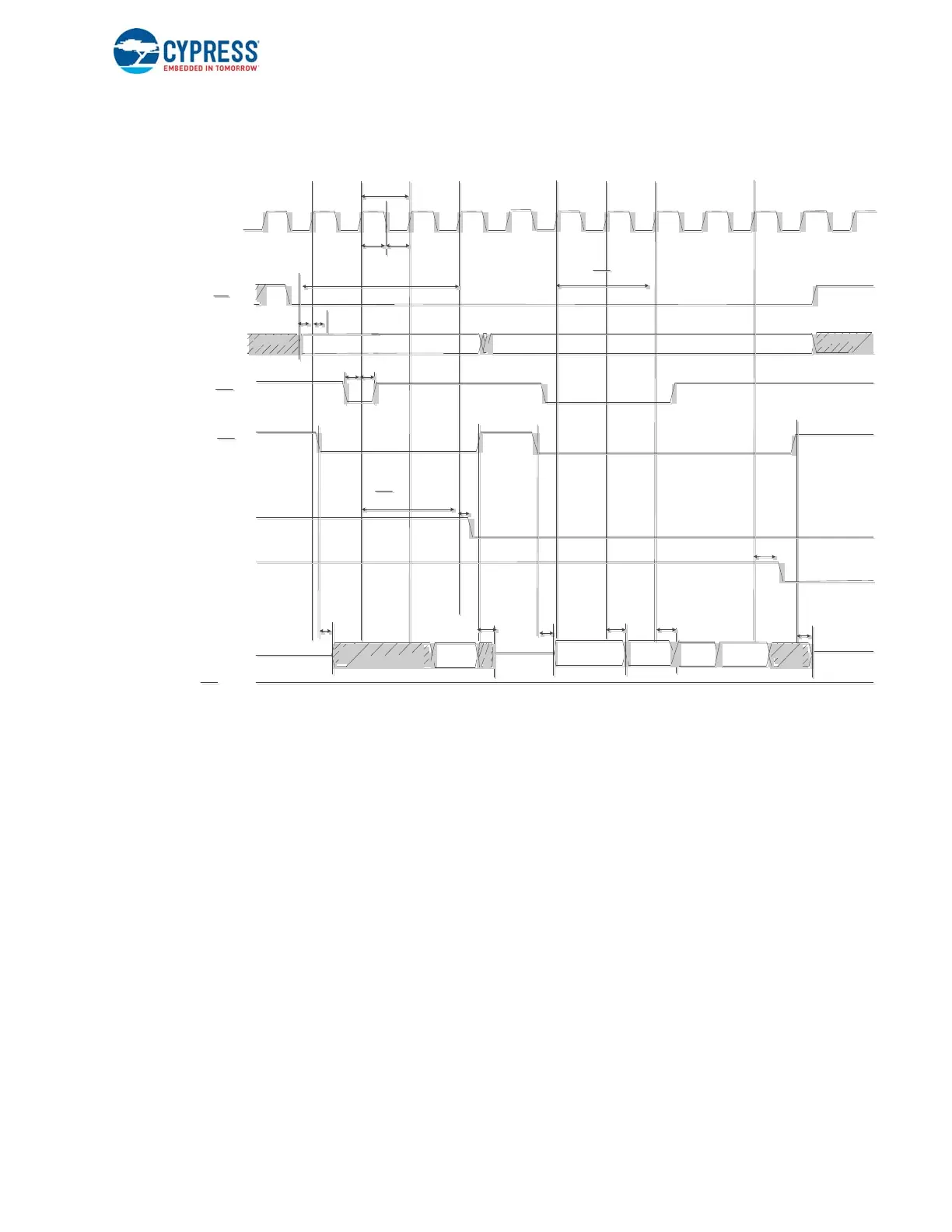

Figure 7-51. Synchronous Slave FIFO Read Sequence

7.16.1 Synchronous Slave FIFO Read Sequence Description

The sequence for performing reads from the synchronous Slave FIFO interface is as follows.

1. The FIFO address is stable and SLCS# is asserted.

2. SLOE# is asserted. SLOE# is an output enable that signals FX3 to drive the data bus.

3. SLRD# is asserted.

The FX3 FIFO pointer is updated on the rising edge of the PCLK, while SLRD# is asserted. This action starts the propagation

of data from the newly addressed FIFO to the data bus. After a propagation delay of tCO (measured from the rising edge of

PCLK), the new data value is present. N is the first data value read from the FX3 FIFO. To drive the data bus, SLOE# must

also be asserted.

The same sequence of events applies to a burst read.

Note: For burst mode, SLRD# and SLOE# are left asserted during the entire duration of the read. When SLOE# is asserted,

the data bus is driven with data from the previously addressed FIFO. For each subsequent rising edge of PCLK, while SLRD#

is asserted, the FIFO pointer is incremented, and the next data value is placed on the data bus.

FLAG Usage: FLAG signals are monitored by the external processor for flow control. FLAG signals are FX3 outputs that may

be configured to show empty/full/partial status for a dedicated thread or the current thread being addressed.

PCLK

FIFOADDR

t

CYC

t

CH

t

CL

t

AS

SLCS

SLRD

t

RDS

t

RDH

SLOE

FLAGA

(dedicatedthreadFlagforAn)

(1=NotEmpty0=Empty)

t

OELZ

DQ(DataOut)

High‐Z

Data

driven:D

N

(An)

t

CDH

t

OEZ

t

OEZ

3cyclelatency

fromaddrtodata

t

CO

t

OELZ

An Am

D

N+1

(An) D

N

(Am)

D

N+1

(Am)

D

N+2

(Am)

SLWR(HIGH)

t

AH

FLAGB

(dedicatedthreadFlagforAm)

(1=NotEmpty0=Empty)

2cyclelatencyfrom

SLRDtodata

t

CFLG

t

CFLG

2cyclelatencyfromSLRD

toFLAG

Loading...

Loading...