EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 277

GCTL_WATCHDOG_CS

0xE0050014

10.5.5 GCTL_WATCHDOG_CS

Watchdog Timers Command and Control Register

This register controls two watchdog timers. Each timer can be used in free-running, interrupt, or reset mode and has a select-

able number of significant bits. The frequency is fixed at 32768 Hz, and counters count down only. Firmware can protect this

register against unwanted writes (see GCTL_WAKEUP_EN).

31 BACKUP_CLK Switches the watchdog clocks from the 32-kHz clock input to a 'backup' 32-kHz clock derived from

the main reference clock using BACKUP_DIVIDER. This field is sticky and cannot change after it is

set to 1. This bit can only be cleared with the RESET# pin or POR.

30:16 BACKUP_DIVIDER[14:0] Divider used to generate a 'backup' 32-kHz clock. This is relevant for systems where no 32-kHz clock

is present as an input signal. The external reference clock (OSCCLK) is divided by

(BACKUP_DIVIDER + 1). In other words, a value of 1 means divided by 2. The behavior of the

divider is undefined when this value is 0. This field must not change after the BACKUP_CLK bit is set.

15:11 BITS1[4:0] Number of least significant bits to be used when checking for counter limit (useful only for

MODE = 1, 2).

10 INTR1 Interrupt signal (Mode 1 only). This bit indicates when the WDOG timer has issued an Interrupt to the

CPU while the system is powered-up. Refer to the GCTL_WAKEUP_EVENT register when the

WDOG timer is used to wake up the system from a power-down state.

continued on next page

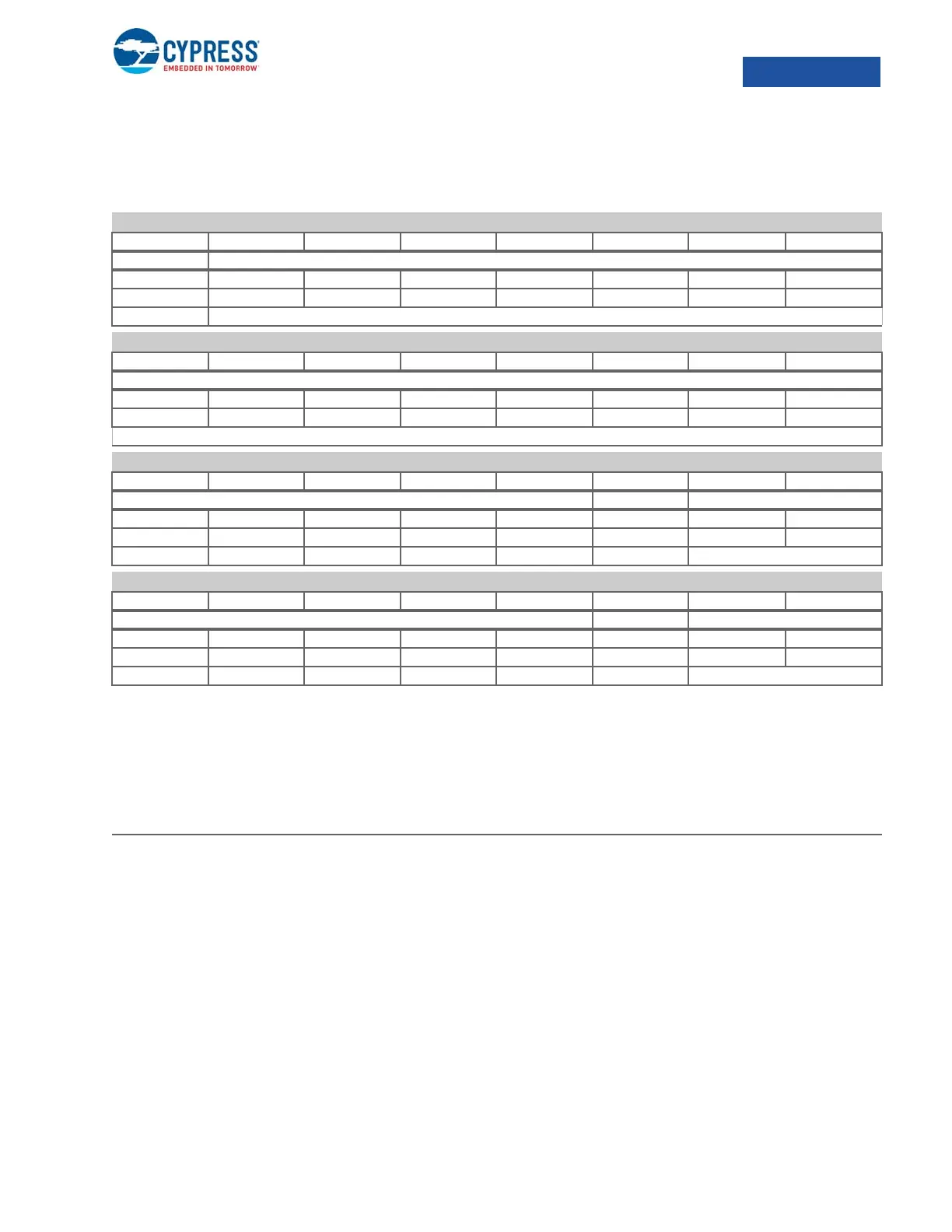

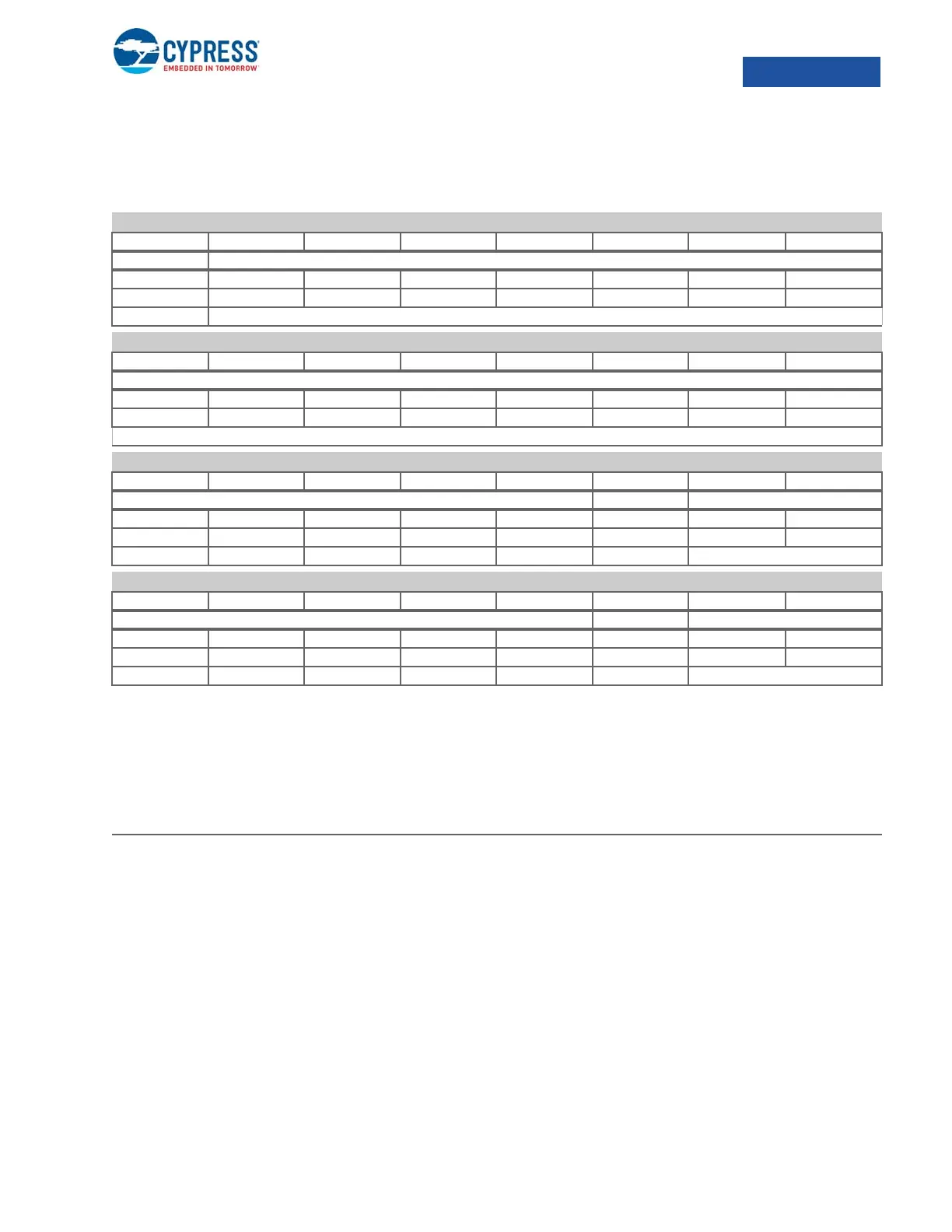

GCTL_WATCHDOG_CS Watchdog Timers Command and Control Register 0xE0050014

b31 b30 b29 b28 b27 b26 b25 b24

BACKUP_CLK BACKUP_DIVIDER[14:8]

R/W1S R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

0

GCTL_WATCHDOG_CS Watchdog Timers Command and Control Register

b23 b22 b21 b20 b19 b18 b17 b16

BACKUP_DIVIDER[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

1

GCTL_WATCHDOG_CS Watchdog Timers Command and Control Register

b15 b14 b13 b12 b11 b10 b9 b8

BITS1[4:0] INTR1 MODE1[1:0]

R/W R/W R/W R/W R/W R/W1C R/W R/W

RRRRRR/W1SRR

000000 3

GCTL_WATCHDOG_CS Watchdog Timers Command and Control Register

b7 b6 b5 b4 b3 b2 b1 b0

BITS0[4:0] INTR0 MODE0[1:0]

R/W R/W R/W R/W R/W R/W1C R/W R/W

RRRRRR/W1SRR

000000 3

Bit Name Description

Loading...

Loading...