EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 169

Low Performance Peripherals (LPP)

■ Capable of multimaster negotiations

■ Supports 100-kHz, 400-kHz, and 1-MHz clock

■ Supports 7-bit and 10-bit addressing modes

■ Supports clock stretching

■ Supports register-based and DMA-based transfers

■ FX3 can boot from I2C EEPROM

Refer to the application note AN76405 - EZ - USB FX3 Boot Options for more information.

8.1.2 I2C Interface Overview

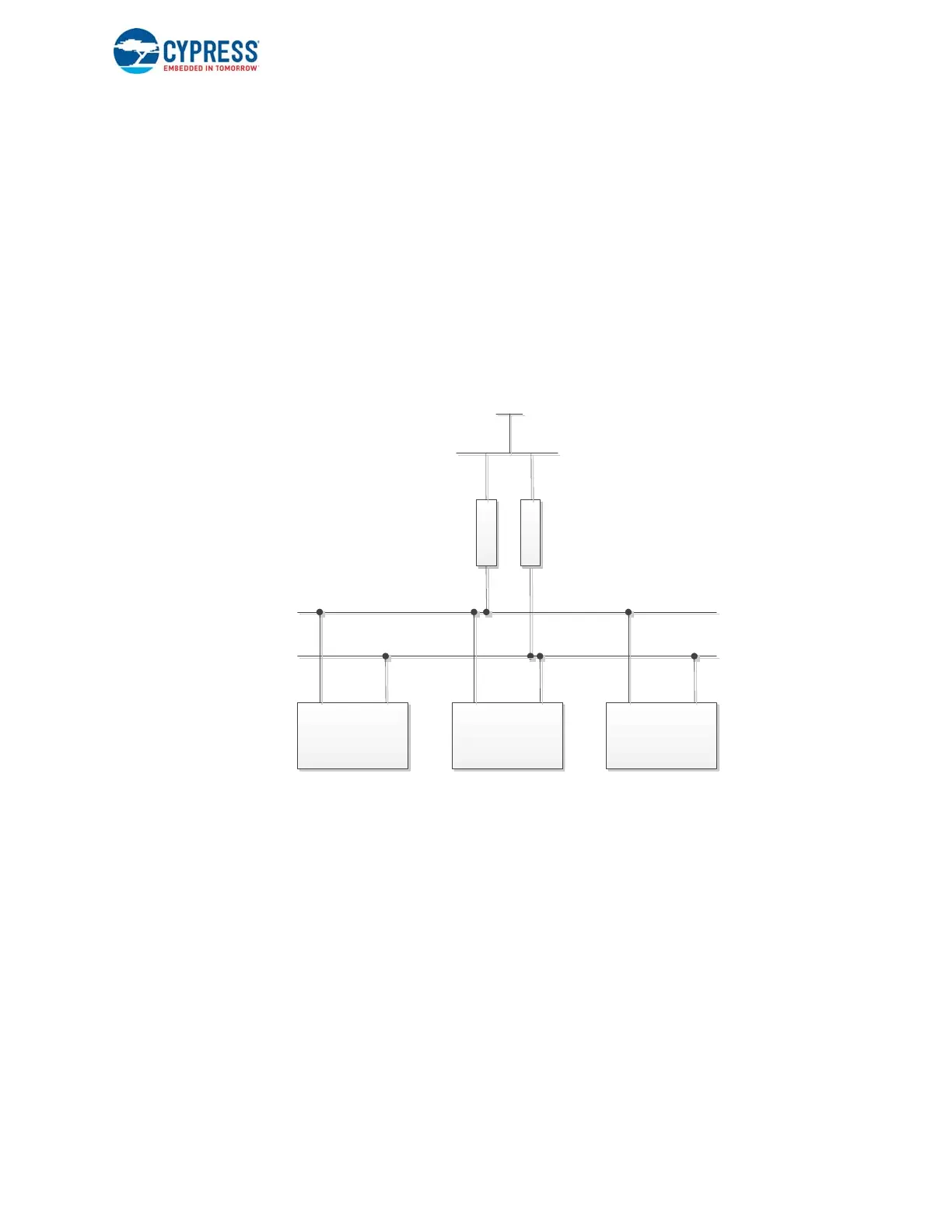

The I²C protocol, created by Philips Semiconductor, allows data to be communicated between I2C devices over two wires. It

sends information serially using one line for data (SDA) and one for clock (SCL), as shown in Figure 8-2.

Figure 8-2. I2C Bus

An I2C master device controls the bus, controlling the clock and generating START/STOP signals that are required for the

communication. I2C slave devices simply listen to the bus and act based on the data sent on the I2C bus. The I2C master can

send data to a slave or receive data from a slave. Slave devices cannot transfer data among themselves. In a single master

system, the master device drives the clock, but slave devices can hold it low to synchronize slow slave devices (clock

stretching). The two signals (SCL and SDA) must be pulled high using external resistors, as they are open collector/drain

outputs and doing so implements a wired AND function. Any device pulling the signal low causes all the devices to see a low

logic value, and for logic high, all devices must stop driving the signal. A slow slave device may need to stop the bus while it

gathers data or services an interrupt. It can do so while holding the clock line (SCL) low, forcing the master into the wait state.

The master must then wait until SCL is released before proceeding. Multimaster mode is used when there is more than one

master on the I2C bus. This mode involves arbitration of the bus and clock synchronization.

FX3 is capable of functioning as a master transceiver and supports 100-kHz, 400-kHz, and 1-MHz operation. The I2C block

operates in big endian mode (most significant bit first) and supports both 7-bit and 10-bit slave addressing. It supports single

and burst (DMA) data transfers. Slow devices on its I2C bus can work with the FX3 I2C master by using clock stretching-

based flow control.

FX3 can function in multimaster I2C bus environments, as it is capable of carrying out negotiations with other masters on the

bus using SDA-based arbitration. Additionally, FX3 supports the repeated START feature to communicate with multiple slave

I2CMaster

Microcontroller

I2CSlave

(EEPROM)

I2CSlave

(RTC)

SDA

SCL

V

R1 R2

Loading...

Loading...