EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 617

DSCR_SYNC

0x24

10.25.8 DSCR_SYNC

Descriptor Synchronization Pointers Register

This register is only modified by the adapter when being read from memory. This register is not intended to be modified by

software directly.

31 EN_PROD_INT Enable generation of a produce event interrupt for this descriptor only. This interrupt will only be seen

by the CPU if SCK_STATUS. int_mask has this interrupt enabled as well. Note that this flag influ-

ences the logging of the interrupt in SCK_STATUS; it has no effect on the reporting of the interrupt to

the CPU similar to the SCK_STATUS.int_mask.

30 EN_PROD_EVENT Enable sending of a produce events from this descriptor only. Events are sent only if SCK_STA-

TUS.en_produce_ev=1. If 0, events will be suppressed, and the descriptor will not be copied back

into memory when completed.

29:24 PROD_IP[5:0] The IP number of the producing socket to which the consume event will be sent. Use 0x3F to desig-

nate ARM CPU (so software) as producer; the event will be lost in this case and an interrupt should

also be generated to observe this condition.

23:16 PROD_SCK[7:0] The socket number of the producing socket to which the consume event will be sent. If prod_ip and

prod_sck matches the socket's IP and socket number then the matching socket becomes consuming

socket.

continued on next page

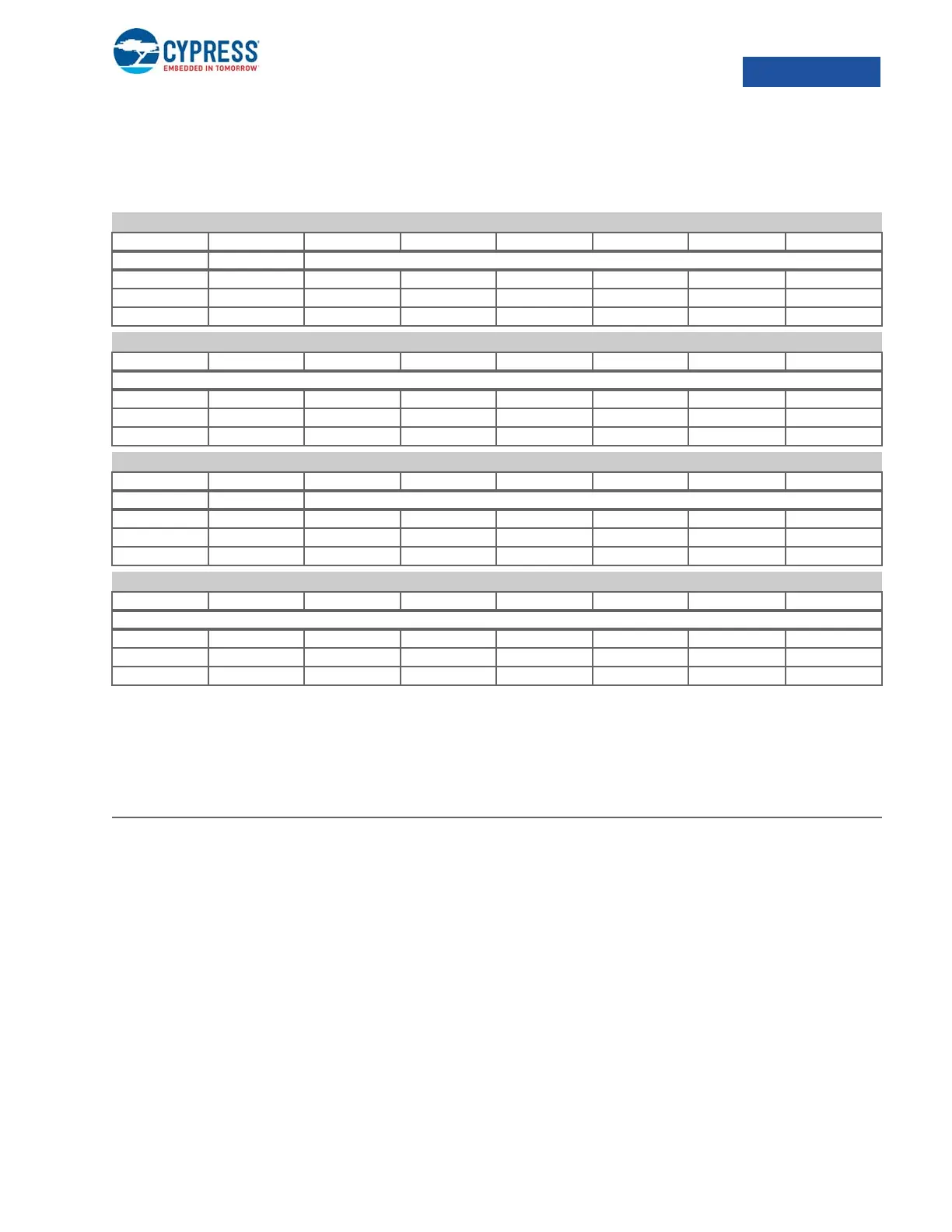

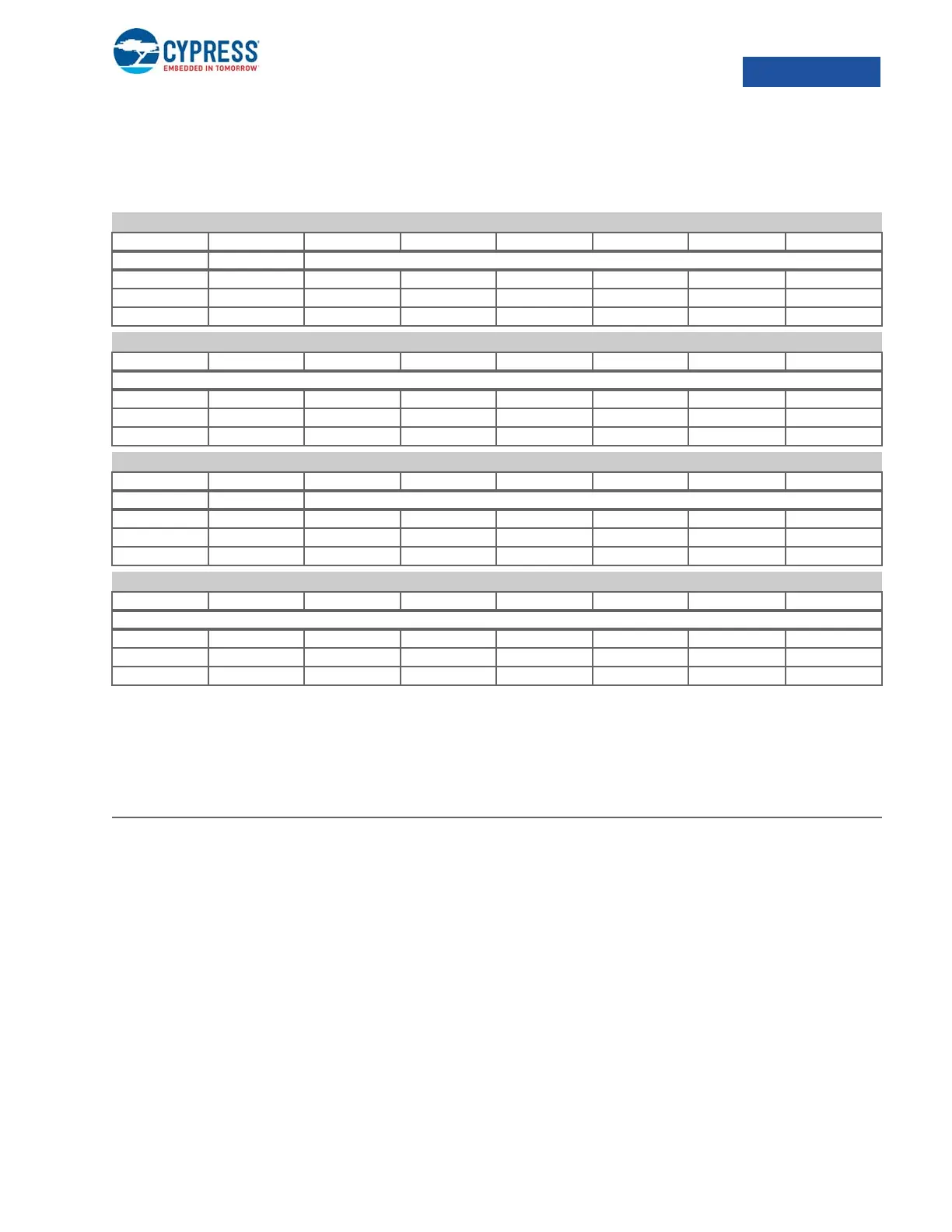

DSCR_SYNC Descriptor Synchronization Pointers Register 0x24

b31 b30 b29 b28 b27 b26 b25 b24

EN_PROD_INT EN_PROD_EVENT PROD_IP[5:0]

R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

XXXXXXXX

DSCR_SYNC Descriptor Synchronization Pointers Register

b23 b22 b21 b20 b19 b18 b17 b16

PROD_SCK[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

XXXXXXXX

DSCR_SYNC Descriptor Synchronization Pointers Register

b15 b14 b13 b12 b11 b10 b9 b8

EN_CONS_INT EN_CONS_EVENT CONS_IP[5:0]

R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

XXXXXXXX

DSCR_SYNC Descriptor Synchronization Pointers Register

b7 b6 b5 b4 b3 b2 b1 b0

CONS_SCK[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

XXXXXXXX

Bit Name Description

Loading...

Loading...