EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 468

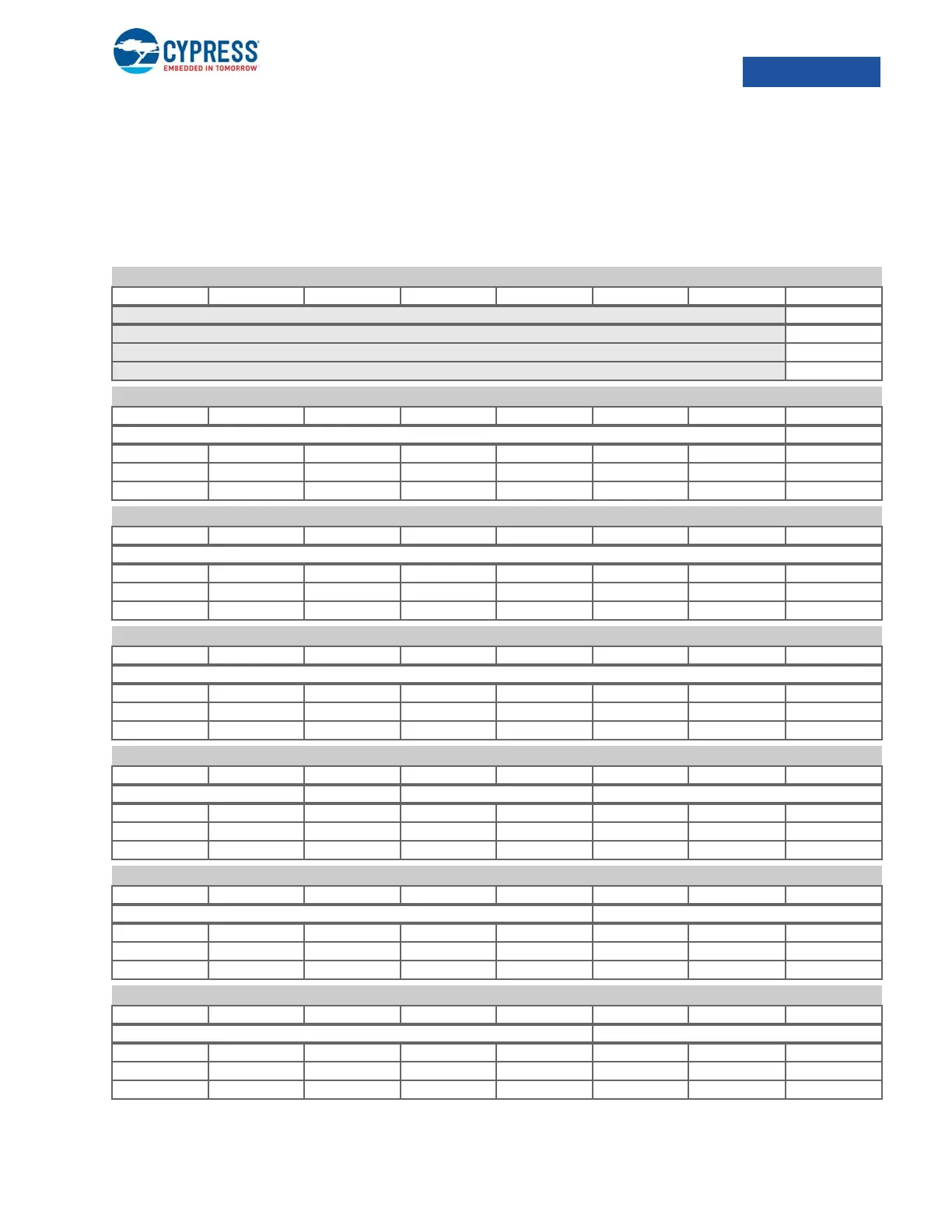

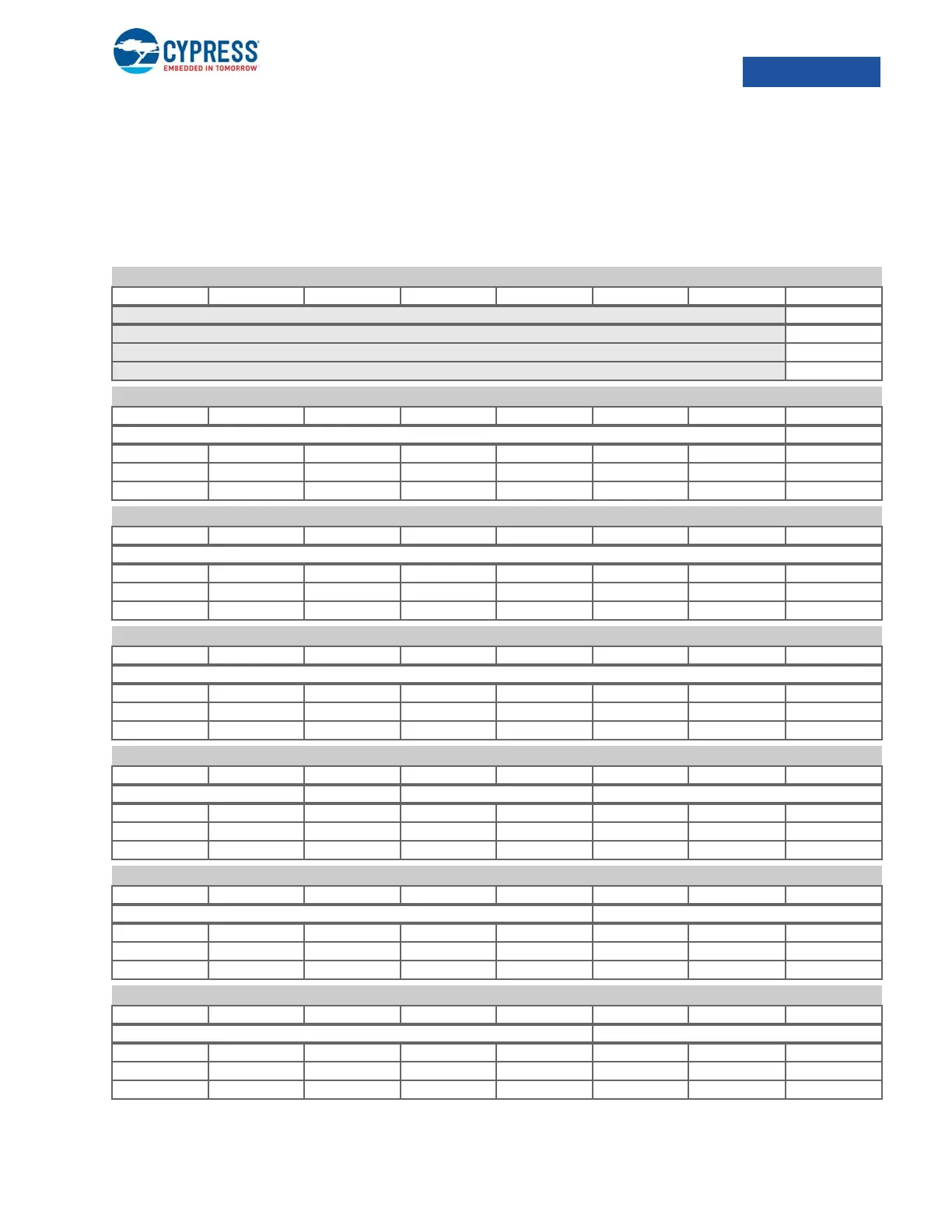

SHDL_EHCI

0xE0032800

10.14.35 SHDL_EHCI

Scheduler Memory Register, EHCI Format

There are 64 SHDL_EHCI registers. The address of each is calculated as SHDL_EHCI(x) = 0xE0032800 + (x*0x4). Hence

SHDL_EHCI(0) is at address 0xE0032800, SHDL_EHCI(1) is at address 0xE0032800 + 0x4 and so on. The definition of each

of these is the same.

continued on next page

SHDL_EHCI Scheduler Memory Register, EHCI Format 0xE0032800

b95 b94 b93 b92 b91 b90 b89 b88

IOC_RATE[7]

R/W

R

0

SHDL_EHCI Scheduler Memory Register, EHCI Format

b87 b86 b85 b84 b83 b82 b81 b80

IOC_RATE[6:0] TRNS_MODE

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

00000000

SHDL_EHCI Scheduler Memory Register, EHCI Format

b79 b78 b77 b76 b75 b74 b73 b72

TOTAL_BYTE_COUNT[15:8]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

00000000

SHDL_EHCI Scheduler Memory Register, EHCI Format

b71 b70 b69 b68 b67 b66 b65 b64

TOTAL_BYTE_COUNT[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

00000000

SHDL_EHCI Scheduler Memory Register, EHCI Format

b63 b62 b61 b60 b59 b58 b57 b56

EP0_CODE[1:0] BYPASS_ERROR MMULT[1:0] RESP_RATE[7:5]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

00000000

SHDL_EHCI Scheduler Memory Register, EHCI Format

b55 b54 b53 b52 b51 b50 b49 b48

RESP_RATE[4:0] POLLING_RATE[7:5]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

00000000

SHDL_EHCI Scheduler Memory Register, EHCI Format

b47 b46 b45 b44 b43 b42 b41 b40

POLLING_RATE[4:0] MAX_PKT_SIZE[10:8]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

00000000

Loading...

Loading...