EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 367

PP_DMA_XFER

0xE0017E2C

10.8.8 PP_DMA_XFER

P-Port DMA Transfer Register

This register is used to set up and control a DMA transfer.

15 DMA_READY Indicates that the link controller is ready to exchange data.

0 Socket not ready for transfer

1 Socket ready for transfer; SIZE_VALID is also guaranteed 1

14 DMA_ERROR 0 No errors

1 DMA transfer error

This bit is set when a DMA error occurs and cleared when the next transfer is started using

DMA_ENABLE = 1.

13 DMA_BUSY Indicates that link controller is busy processing a transfer. A zero length transfer would cause

DMA_READY to never assert.

0 No DMA is in progress

1 DMA is busy

12 SIZE_VALID Indicates that DMA_SIZE value is valid and corresponds to the socket selected in PP_DMA_XFER.

SIZE_VALID will be 0 for a short period after PP_DMA_XFER is written into. AP will poll SIZE_VALID

or DMA_READY before reading DMA_SIZE.

10 LONG_TRANSFER 0 Short transfer (DMA_ENABLE clears at end of buffer

1 Long Transfer (DMA_ENABLE must be cleared by AP at end of transfer)

9DMA_DIRECTION 0 Read (Transfer from FX3 – Egress direction)

1 Write (Transfer to FX3 – Ingress direction)

8 DMA_ENABLE 0 Disable ongoing transfer. If no transfer is ongoing ignore disable

1 Enable data transfer

7:0 DMA_SOCK[7:0] Processor specified socket number for data transfer

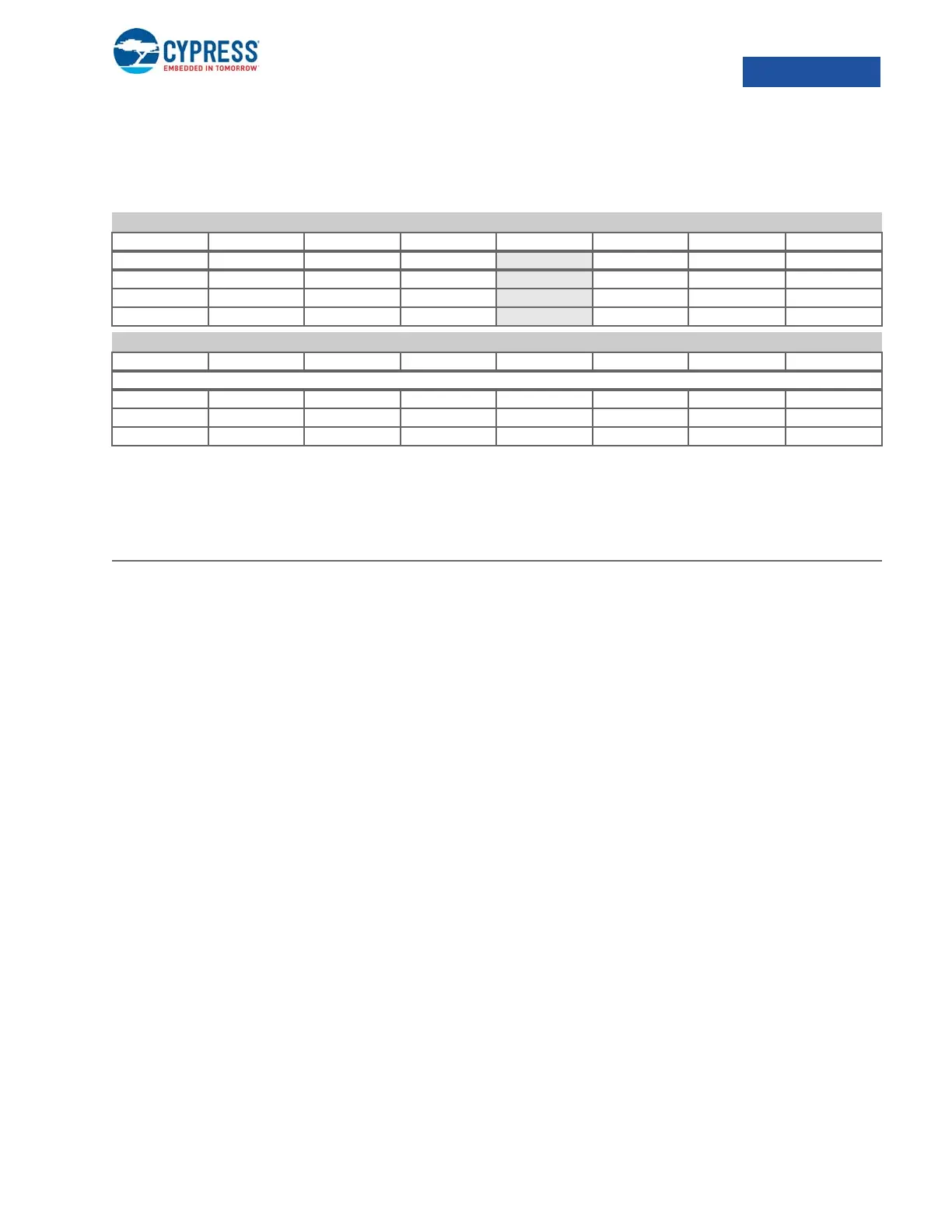

PP_DMA_XFER P-Port DMA Transfer Register 0xE0017E2C

b15 b14 b13 b12 b11 b10 b9 b8

DMA_READY DMA_ERROR DMA_BUSY SIZE_VALID LONG_TRANSFER DMA_DIRECTION DMA_ENABLE

RRRR R/W R/W R/W

WWWR/W

RRR/W

0000

000

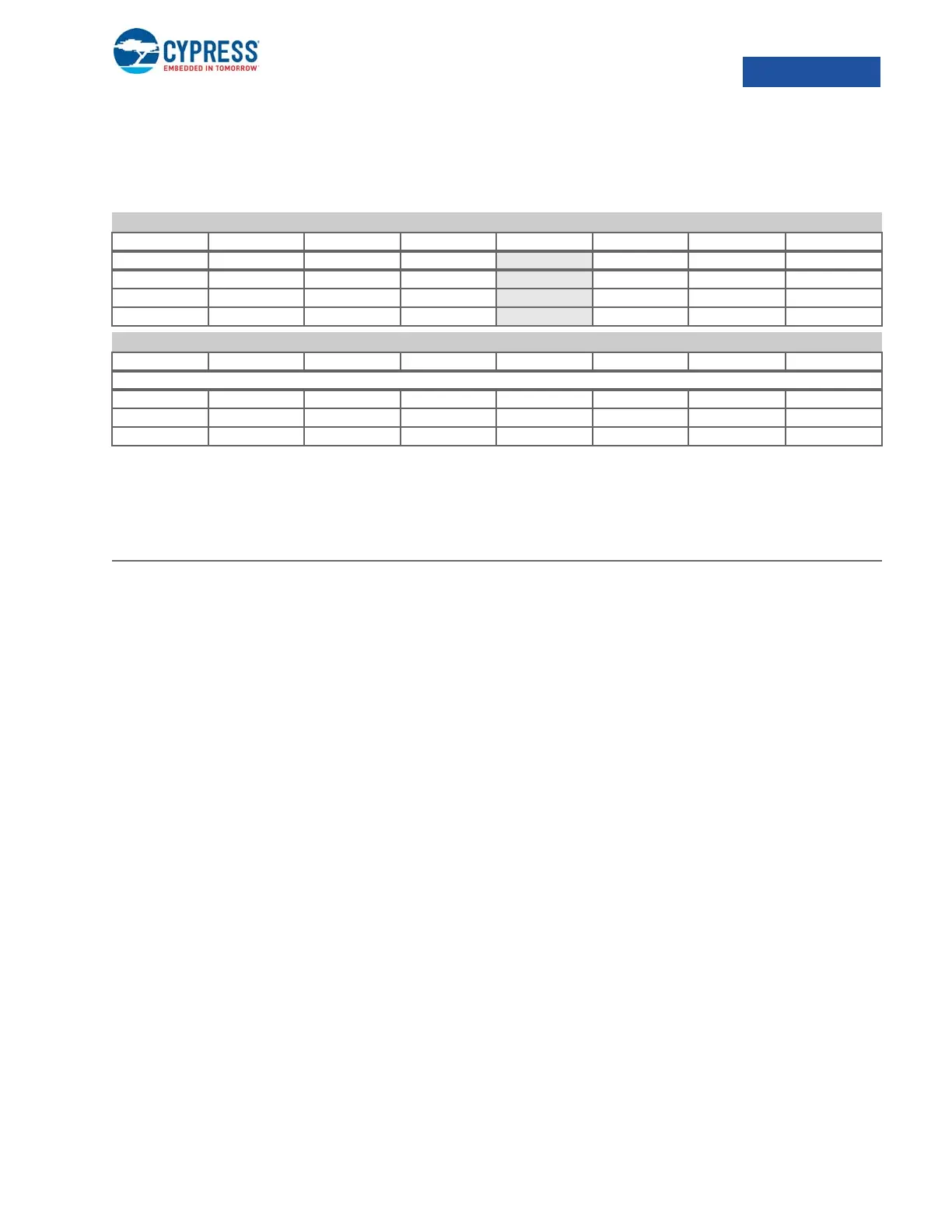

PP_DMA_XFER P-Port DMA Transfer Register

b7 b6 b5 b4 b3 b2 b1 b0

DMA_SOCK[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

00000000

Bit Name Description

Loading...

Loading...