EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 644

SDMMC_MODE_CFG

0xFC

10.26.17 SDMMC_MODE_CFG

SD/MMC Mode Configuration Register

Configures clock, signaling, and so on for each of the storage ports. There are two copies of this register corresponding to the

two storage ports. The address of each register is calculated as 0xe0020030 + (port * 0x0400).

31 IDLE_STOP_CLK_EN 0: Do not stop clock automatically after each command.

1: Stop clock automatically IDLE_STOP_CLK_DELAY cycles after each command.

Clock is not stopped if the card indicates busy and stopped when the card gets out of busy.

30:24 IDLE_STOP_CLK_DELAY Number of clock cycles delay after the completion of the last command after which the clock will be

stopped. This value may be changed only when IDLE_STOP_CLK_EN is 0.

22 EXP_BOOT_ACK 1: Boot acknowledgement is expected when booting from eMMC.

0: Boot acknowledgement is not expected.

21 BLK_END_STOP_CLK 0: SDMMC interface clock can be stopped at any time when data overflow/underflow is detected.

1: SDMMC interface clock can be stopped only at the end of data block transfer. Clock is not stopped

in the middle of a block data transfer.

It is recommended that this bit should be set to 1.

continued on next page

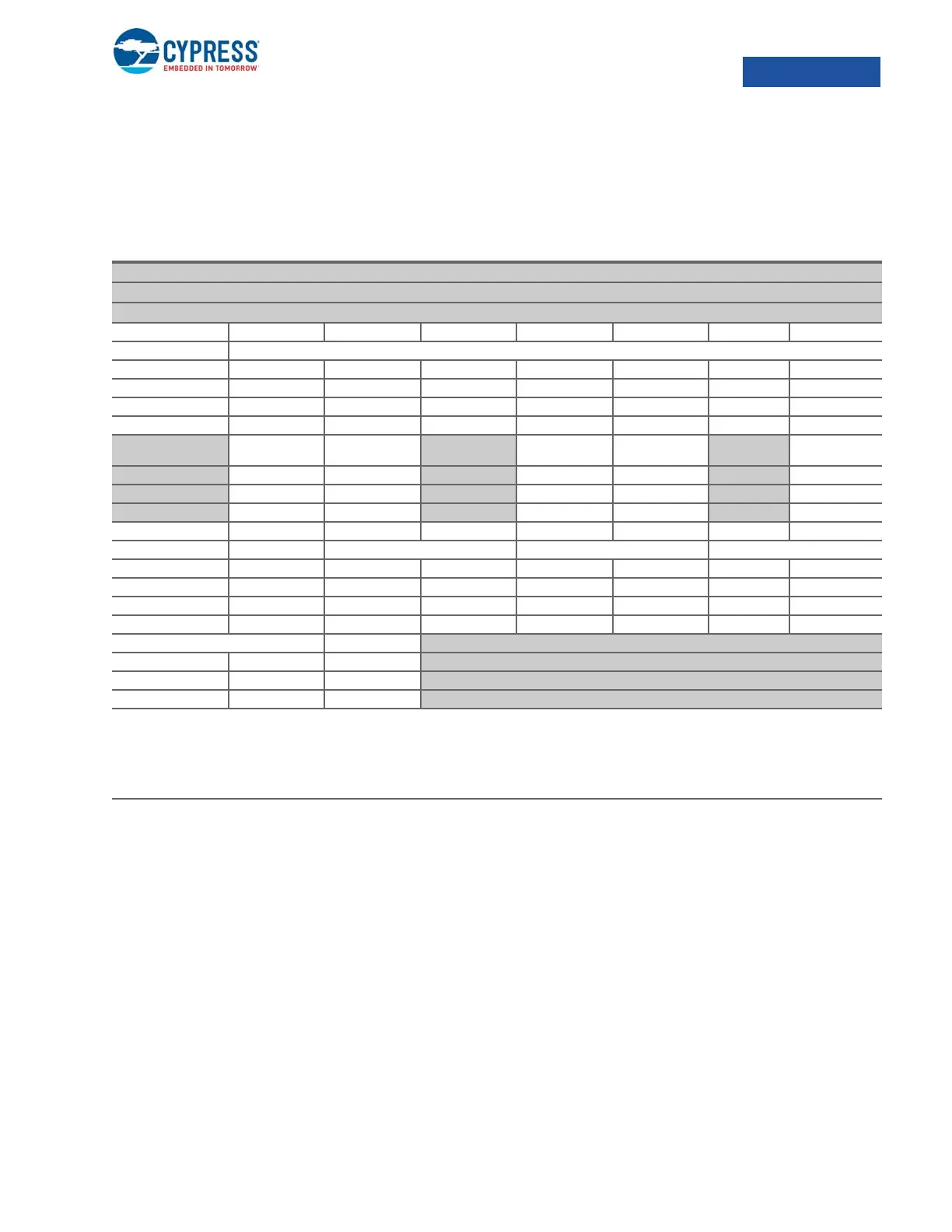

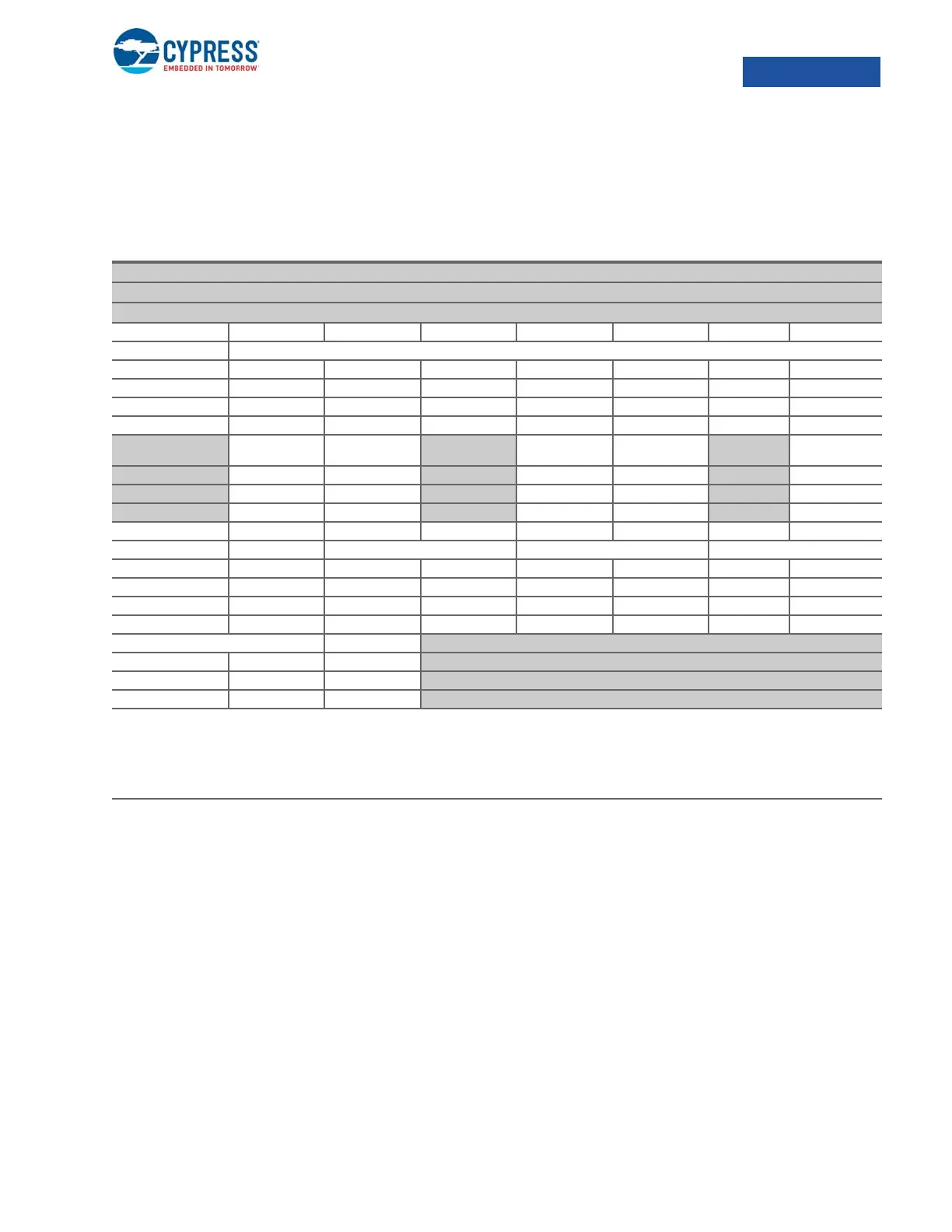

SDMMC_MODE_CFG

SDMMC Mode Configuration

0xE0020030

b31 b30 b29 b28 b27 b26 b25 b24

IDLE_STOP_CLK_EN IDLE_STOP_CLK_DELAY[6:0]

R RRRRRRR

R/W R/W R/W R/W R/W R/W R/W R/W

0 0010000

b23 b22 b21 b20 b19 b18 b17 b16

EXP_BOOT_ACK

BLK_END_STOP

_CLK

RD_END_STOP_

CLK_EN

CARD_DETECT_

POLARITY

WR_STOP_CLK_

EN

RR RR R

R/WR/W R/WR/W R/W

00 00 0

b15 b14 b13 b12 b11 b10 b9 b8

RD_STOP_CLK_EN EN_CMD_COMP DATABUSWIDTH[1:0] MODE[1:0] SIGNALING[3:2]

R RRRRRRR

R/W R/W R/W R/W R/W R/W R/W R/W

0 0000100

b7 b6 b5 b4 b3 b2 b1 b0

SIGNALING[1:0] DLL_BYPASS_EN

RRR

R/W R/W R/W

001

Bit Name Description

Loading...

Loading...