EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 268

GCTL_SPI_CORE_CLK

0xE005202C

10.4.19 GCTL_SPI_CORE_CLK

SPI Core Clock Configuration Register

31 CLK_EN Enable clock divider. Both the divider itself and its output are gated.

18:17 SRC[1:0] Clock source select. This field selects between one of the following four prestage system clocks:

00 sys16_clk (sys_clk_pll divided by 16)

01 sys4_clk (sys_clk_pll divided by 4)

10 sys2_clk (sys_clk_pll divided by 2)

11 sys_clk_pll

16 HALFDIV Nonintegral divider select. This field adds 0.5 to the divider value selected by the DIV field. This yields

divider values from 2.5 to 65536.5.

15:0 DIV[15:0] Clock divider value. This determines how much to divide the PLL system clock. The actual divider is

DIV + 1. Zero (divide by 1) is illegal and results in undefined behavior. In other words, the range of

divider values is 2 to 65536.

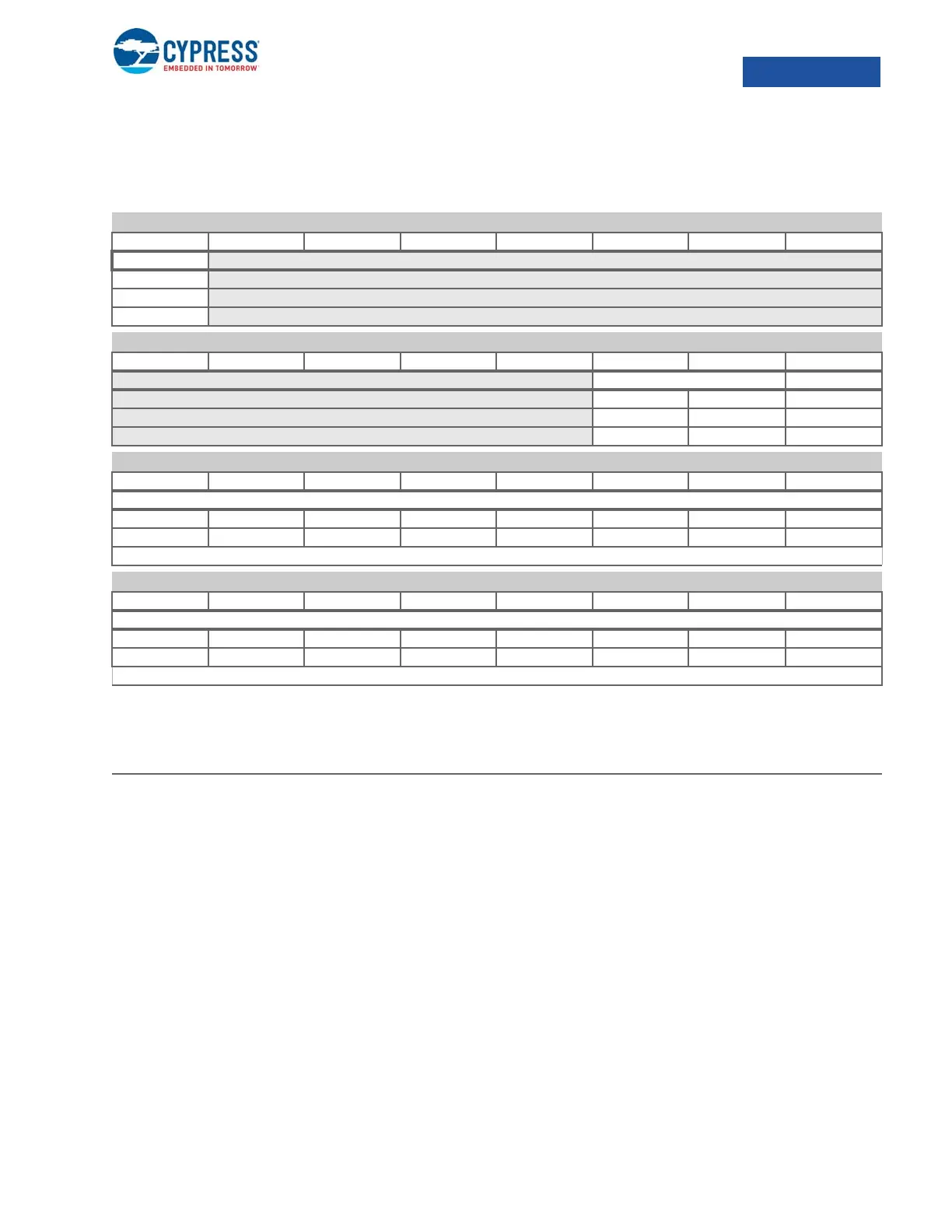

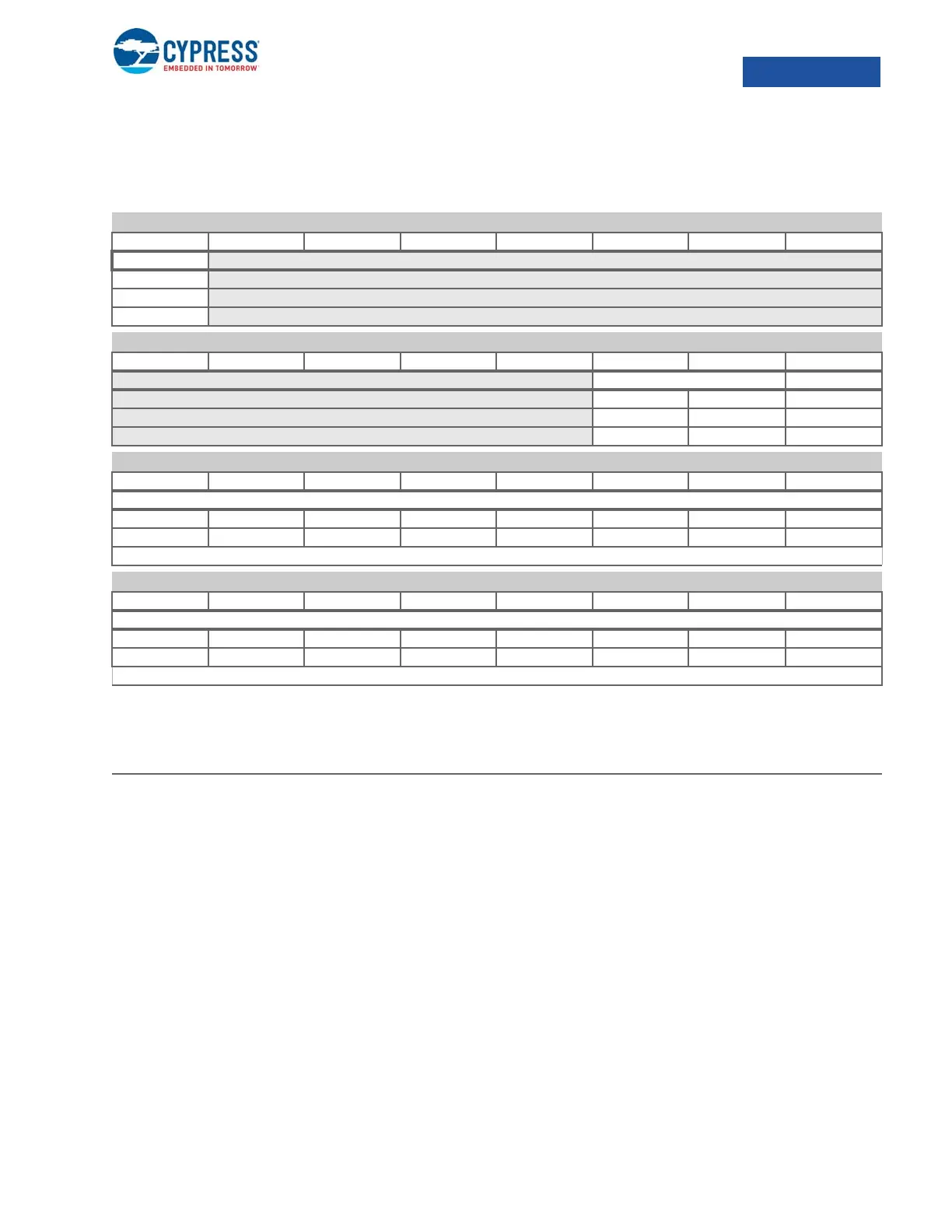

GCTL_SPI_CORE_CLK SPI Core Clock Configuration Register 0xE005202C

b31 b30 b29 b28 b27 b26 b25 b24

CLK_EN

R/W

R

0

GCTL_SPI_CORE_CLK SPI Core Clock Configuration Register

b23 b22 b21 b20 b19 b18 b17 b16

SRC[1:0] HALFDIV

R/W R/W R/W

RRR

000

GCTL_SPI_CORE_CLK SPI Core Clock Configuration Register

b15 b14 b13 b12 b11 b10 b9 b8

DIV[15:8]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRR

R R R R

GCTL_SPI_CORE_CLK SPI Core Clock Configuration Register

b7 b6 b5 b4 b3 b2 b1 b0

DIV[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

R R R R R R R R

1

Bit Name Description

Loading...

Loading...