EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 360

PP_INIT

0xE0017E04

10.8.2 PP_INIT

P-Port Reset and Power Control Register

This register is used for reset and power control and determines endian orientation of the P-port.

15 BIG_ENDIAN 0 P-Port is Little Endian

1 P-Port is Big Endian

11 HARD_RESET_N Software clears this bit to effect a global hard reset (all blocks, all flops). This is equivalent to toggling

the RESET pin on the device. This function is also available to internal firmware in GCTL_CONTROL.

10 CPU_RESET_N Software clears this bit to effect a CPU reset (aka reboot). No other blocks or registers are affected.

The CPU will enter the boot ROM, that will use the WARM_BOOT flag to determine whether to reload

firmware.

Unlike the same bit in GCTL_CONTROL, the software needs to explicitly clear and then set this bit to

bring the internal CPU out of reset. It is permissible to keep the ARM CPU in reset for an extended

period of time (although not advisable).

4 WAKEUP_CLK Indicates system woke up from suspend state. If firmware does not clear this bit it will stay 1 even

through standby sequences. This bit is a shadow bit of GCTL_CONTROL.

3 WAKEUP_PWR Indicates system woke up from standby mode. If firmware does not clear this bit it will stay 1 even

through suspend sequences. This bit is a shadow bit of GCTL_CONTROL.

2 WDT_RESET Indicates system woke up from a watchdog timer induced hard reset (see GCTL_WATCHDOG_CS).

If firmware does not clear this bit it will stay 1 even through standby and suspend sequences. This bit

is a shadow bit of GCTL_CONTROL.

1 SW_RESET Indicates system woke up from a software induced hard reset sequence (from GCTL_CON-

TROL.HARD_RESET_N or PP_INIT.HARD_RESET_N). If firmware does not clear this bit it will stay

1 even through standby and suspend sequences. This bit is a shadow bit of GCTL_CONTROL.

0POR Indicates system woke up through a power-on-reset or RESET# pin reset sequence. If firmware does

not clear this bit it will stay 1 even through software reset, standby and suspend sequences. This bit

is a shadow bit of GCTL_CONTROL.

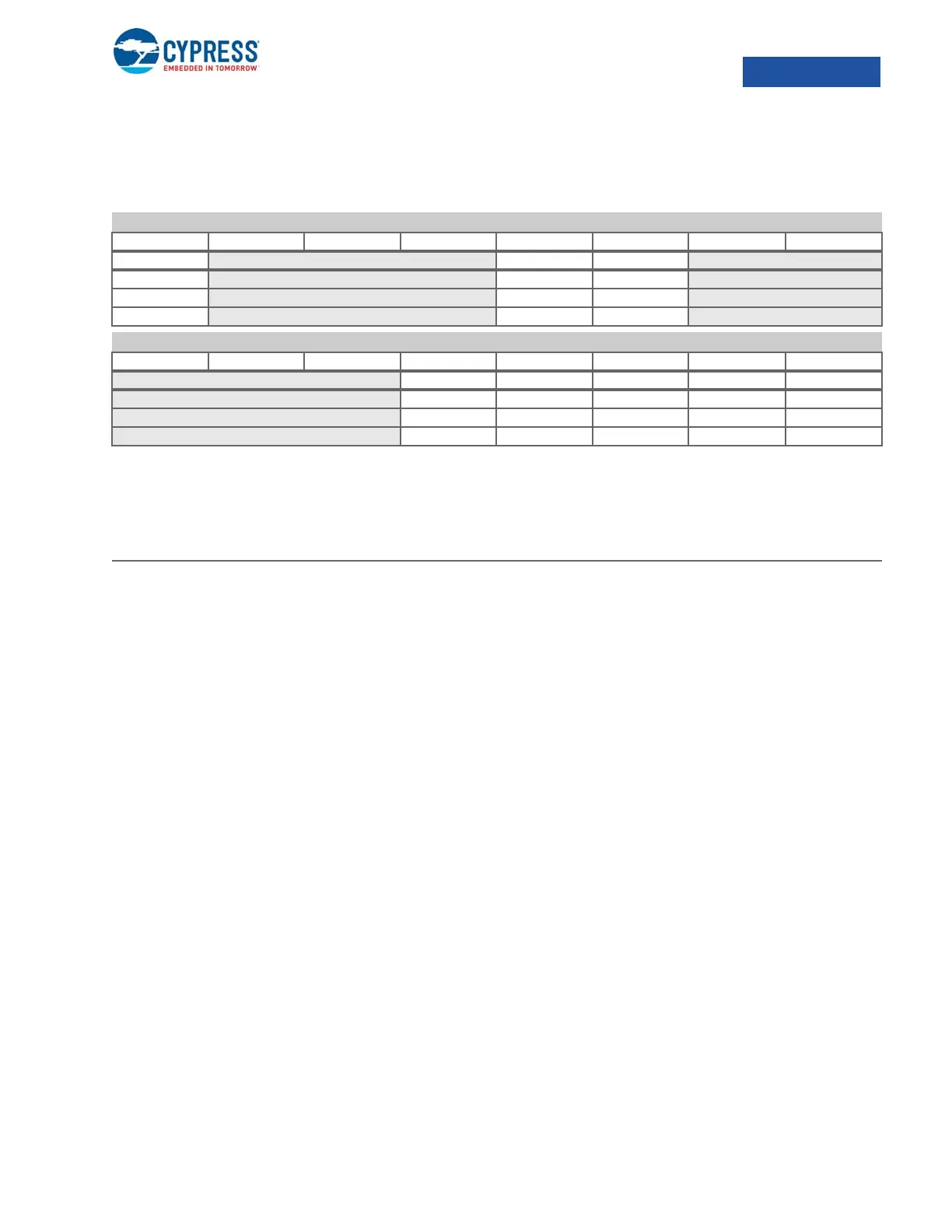

PP_INIT P-Port Reset and Power Control Register 0xE0017E04

b15 b14 b13 b12 b11 b10 b9 b8

BIG_ENDIAN HARD_RESET_N CPU_RESET_N

R/W R/W0C R/W

R RR

0 11

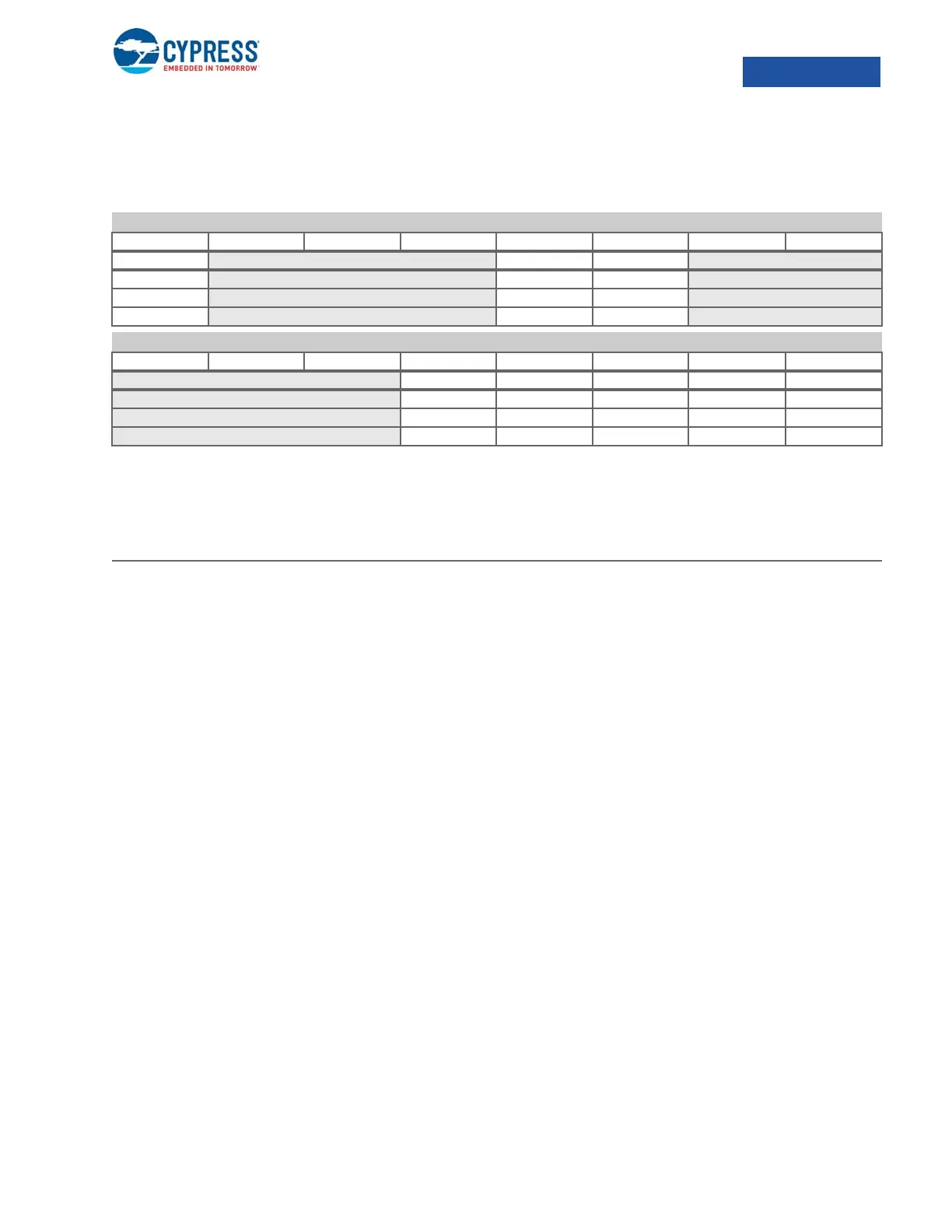

PP_INIT P-Port Reset and Power Control Register

b7 b6 b5 b4 b3 b2 b1 b0

WAKEUP_CLK WAKEUP_PWR WDT_RESET SW_RESET POR

RRRR/WR/W

R/W R/W R/W R R

00001

Bit Name Description

Loading...

Loading...