EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 122

General Programmable Interface II (GPIF II)

The GPIF II interface offers a maximum of 32 bidirectional data lines:

■ An 8-bit-wide GPIF II interface (DQ[7:0]) uses pins GPIO[7:0].

■ A 16-bit-wide GPIF II interface (DQ[15:0]) uses pins GPIO[15:0].

■ A 24-bit-wide GPIF II interface (DQ[23:0]) uses pins GPIO[40:33] and GPIO[15:0].

■ A 32-bit-wide GPIF II interface (DQ[31:0]) uses pins GPIO[49:46], GPIO[44:33], and GPIO[15:0].

GPIF II can function as a master or slave. If it is configured as a master, then the GPIOs remaining after allocating for the data

bus and control signals can be used as address lines. If GPIF II is configured as a slave, then the maximum number of

address lines is limited to eight.

The interface clock, PCLK, can be configured as either an input or an output interface clock for synchronous interfaces to

external logic. The maximum frequency supported for the GPIF II interface clock is 100 MHz.

7.4 Functional Overview

The GPIF II interface is configured by creating a GPIF II state machine, and 8 KB of memory space is allocated to store the

GPIF II state machine definition. Each state is defined by 32 bytes in (SRAM) memory. These 32 bytes define the properties

of a state and the trigger conditions that can cause state (or I/O) transitions. Each state has two transitions out of it. The

transition out of a state is determined based on transition conditions. Transitions are caused by both external and internal

triggers. Each state is programmed to perform certain actions. The transition conditions are checked on each GPIF II clock

edge or after a programmable number of clock cycles.

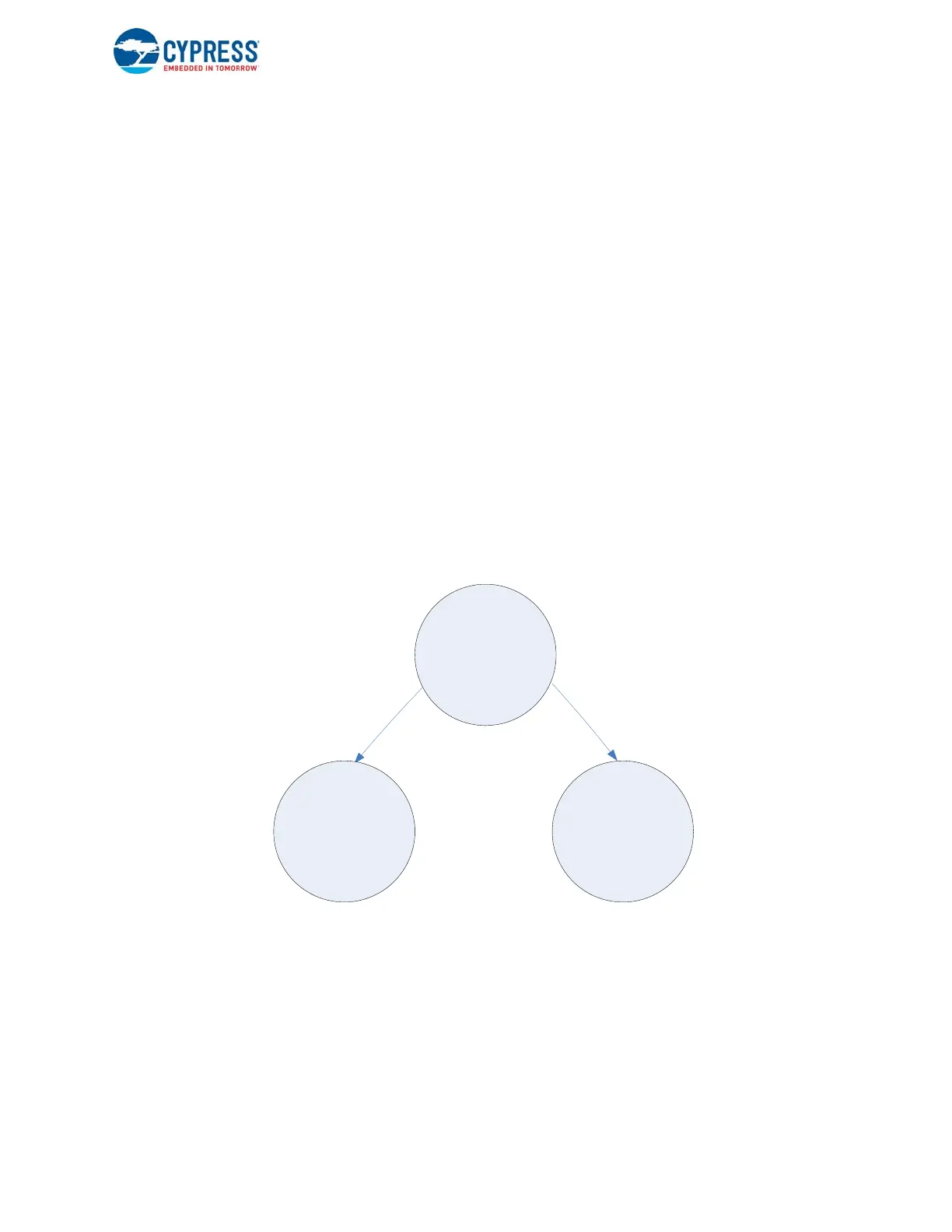

Figure 7-3 is a simple depiction of the basic structure of a GPIF II state.

Figure 7-3. Structure of a GPIF II State

7.4.1 Actions

Each state in a GPIF II state machine can be programmed to perform one or more actions. Actions performed in a state can

be programmed to be performed once or repeated in every clock cycle until a state change occurs. Actions can be internal,

such as reading or writing to a buffer. They can also be external, such as driving an output high or low. Ta b l e 7- 2 lists the

GPIF II actions.

State 1

(Assert Actions for

State1)

If (f0*) then transition left

If (f1*) then transition right

State 2

(Assert Actions for

State2)

State 3

(Assert Actions for

State3)

Notes:

- * f0 and f1 are logical functions of triggers

- f0 is checked first. If f0 = TRUE, then GPIFII transitions from State 1 to State 2. If f0 = FALSE, then f1

is checked.

- If f1 = TRUE, then GPIFII transitions from State 1 to State 3.

- If both f0 and f1 evaluate to FALSE, then GPIFII remains in State 1. At the next clock, the conditions

are checked again.

Loading...

Loading...