EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 89

Universal Serial Bus (USB)

6.7 USB 2.0 Function

6.7.1 Clocking

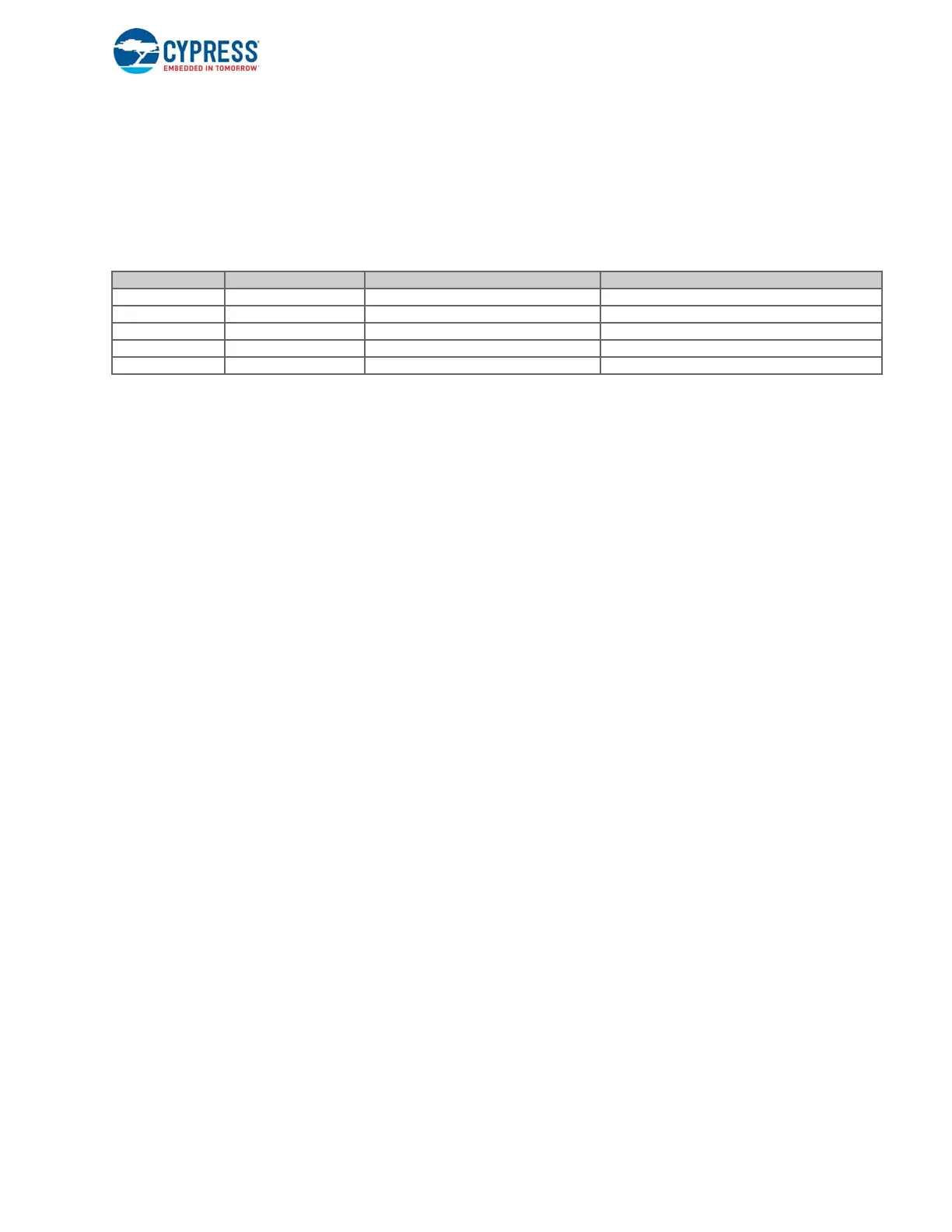

There are five independent clock domains in the UIB block supporting the USB 2.0 function, as listed in Table 6- 3 .

Table 6-3. USB 2.0 Function Clocks

In addition, the EPM uses a clock uib_epm_clk_i that is 100 MHz when the USB 2.0 function controller is active. The

uib_epm_clk_i configuration source is from GCTL_UIB_CORE_CLK.EPMCLK_SRC and enabled by

GCTL_UIB_CORE_CLK.CLK_EN.

6.7.2 Interrupt Requests

The UIB block has three global interrupt sources to the VIC, listed in Table 6-2, which are shared among USB 3.0, USB 2.0

and OTG controllers.

UIB has a global interrupt register, UIB_INTR, which contains interrupt sources from the respective functional blocks (USB

3.0 function, USB 2.0 function, USB 2.0 host, USB 2.0 OTG, charger detect, EPM). The UIB core interrupt to VIC is the logical

OR of interrupt sources in UIB_INTR.

USB 2.0 function controller interrupts are located in UIB_DEV_CTL_INTR. UIB_INTR.DEV_CTL_INT is the logical OR of the

interrupt sources in UIB_DEV_CTL_INTR.

USB 2.0 function endpoint interrupts are located in UIB_DEV_EP_INTR. UIB_INTR.DEV_EP_INT is the logical OR of the

interrupt sources in UIB_DEV_EP_INTR.

6.7.3 USB 2.0 Functional Description

The USB 2.0 function controller hardware includes an a Serial Interface Engine (SIE) and Token Processor (TP). It does the

following:

■ Handles the handshake between the endpoint and the host device

■ Generates an interrupt when valid data packets are received

■ Generates an interrupt when an error in transmission occurs

■ Moves valid data to/from the endpoint

■ Handles all the bit stuffing required

6.7.3.1 Serial Interface Engine

The SIE is responsible for handling the USB traffic at the byte-level and for detecting the suspend, reset, and resume USB

bus states. It parses the traffic, decoding the types of packets that have been received and translating the packet types into

bytes for transmission back to the host on the USB bus.

6.7.3.2 Token Processor

The TP handles most of the protocol described in chapter 8 of the USB specification. It receives the USB basic protocol

commands from the host and generates the appropriate sequence of responses by synchronizing the frame timer, receiving/

Domain Typ Freq Configuration Source Description

dma_bus_clk_i 100 MHz GCTL_CPU_CLK_CFG.DMA_DIV DMA access clock

mmio_bus_clk_i 100 MHz GCTL_CPU_CLK_CFG.MMIO_DIV MMIO register access clock

uib_sieclock_i 30 MHz Driven from USB 2.0 OTG PHY USB 2.0 serial interface engine clock

standby_clk_i 32 kHz Always-on Always-on clock for low-power modes

uib_ref_clk_i 19.2/26/38.4/52 MHz External input clock USB 2.0 PHY reference clock

Loading...

Loading...