EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 110

Universal Serial Bus (USB)

1. The device disconnect is detected by the host TP, which signals the EHCI interface. The UIB_HOST_EH-

CI_PORTSC:PORT_CONNECT_C field (and through that the UIB_HOST_EHCI_USBSTS:PORT_CHNG_DET field)

generates an interrupt request.

2. At the same time, the UIB_HOST_EHCI_PORTSC:PORTOWNER field is cleared, transferring port ownership to the EHCI

interface.

3. After disconnect, the EHCI interface resumes its role as the default port owner.

6.9.11.3 Managing Transfers

The USB 2.0 host hardware scheduler reads elements from the scheduler memory and based on its fields along with the EPM

status, it decides to schedule the element for SIE. The result of the executed transaction is recorded in the status fields. The

status of all the transactions for that scheduler entry are recorded as "sticky" in the status field until the scheduler entry is

complete.

Every entry in the scheduler memory represents one queue head (QH) in EHCI terminology or endpoint descriptor (ED) in

OHCI terminology. From this point on, this document calls it "QH" for convenience. In the fetch QH, one entry of the scheduler

memory is read. If that entry cannot be scheduled for the SIE due to halt bit set or entry not active, then the scheduler skips

and next QH. The software updates the active bit in the scheduler memory only during the scheduler memory update. The

active bit is set to zero when the host controller successfully executes the total_byte_cnt of transactions. The USB 2.0 host

controller reports the active/nonactive condition through the status bits. The bus scheduler does not execute a QH when its

active bit is zero.

The status of the USB transactions is written directly into system memory based on the response rate written in scheduler

memory per endpoint. The base address where scheduler responses are written is programmed via

HOST_RESP_BASE.BASE_ADDRESS. The response condition is programmed via the HOST_RESP_CS register. The

response rate indicates after how many either successful transactions or not NAKed transactions the status should be written

into system memory for the software to process. The firmware can use the UIB_HOST_RESP_CS.WR_RESP_COND

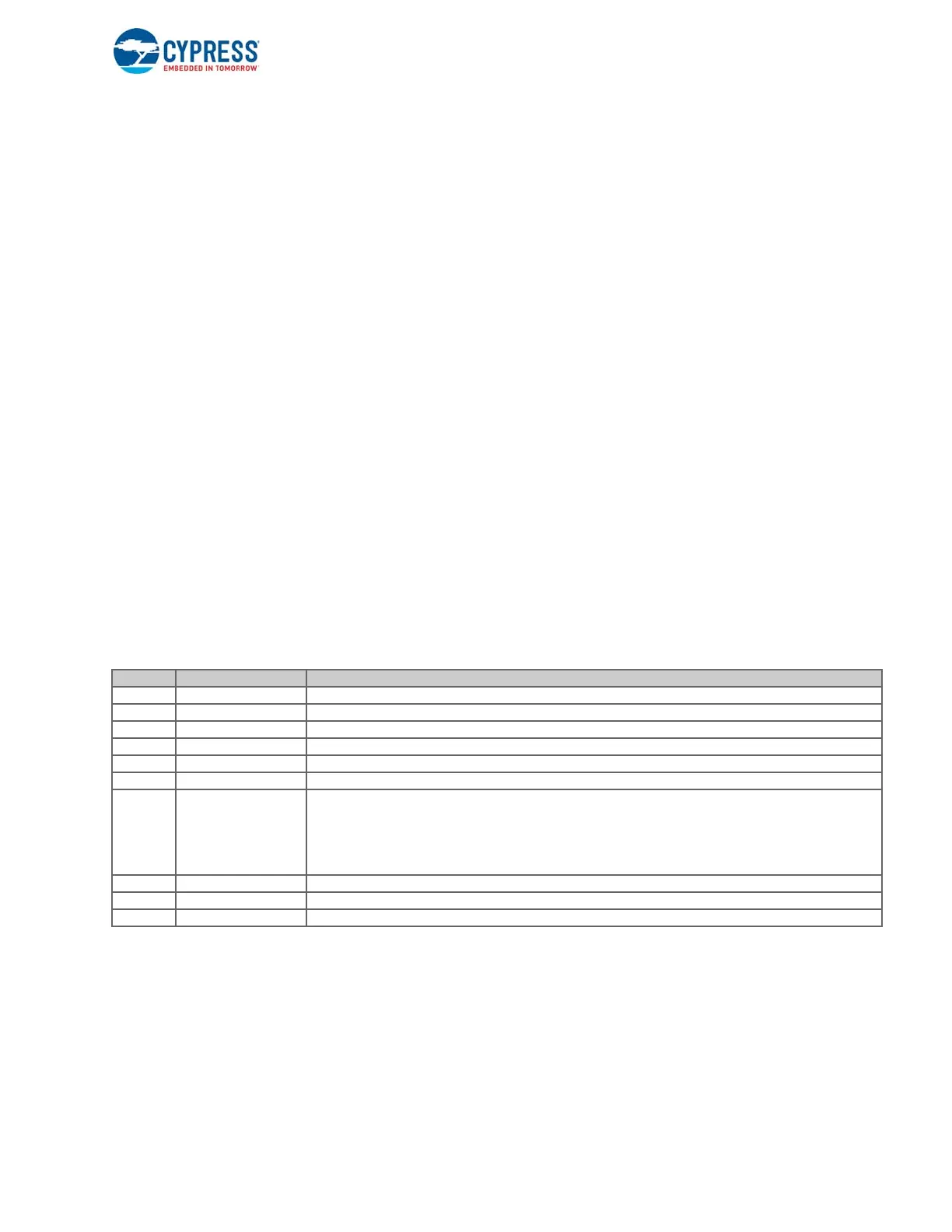

register bit to decide on the successful or not NAKed transactions. Table 6-5 provides a description of the status.

Table 6-5. USB 2.0 Host Response

6.9.11.3.1 Control Transfer Specific

An EP0 control transfer falls into three categories:

Setup transaction: N number of OUT data transactions followed by 1 IN token (ZLP)

Setup transaction: N number of IN data transactions followed by 1 OUT token (ZLP)

Setup transaction: 1 IN token (ZLP)

Bit Name Description

3:0 EP_NUM Endpoint number

4 Direction 0: IN 1: Out

5 Active 0: EP got deactivated. 1: EP is still active.

6 Halt 1: EP is not halted. 2: EP is halted.

7 Overrun/ Underrun 0: No overrun/underrun condition 1: There was an overrun/underrun when accessing the EPM.

8 Babble 0: No babble is detected. 1: Babble was detected.

9XactErr

PhyErr or CRC16 error, or device times out, or PID error or IN-ISO XactError IN-ISO XactErr:

The first transaction for the IN ISO has a data toggle equal, or

More than the MULT field is specified in the scheduler memory, or

There is a data toggle mismatch in the transaction excluding the first transaction, or

A short IN-ISO with a data toggle greater than one was received.

10 Ping 0: No ping token has been issued. 1: Ping token has been issued when enabled.

15:11 - Reserved

31:16 Byte Count Total byte count left

Loading...

Loading...