EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 255

GCTL_IOPOWER_INTR_MASK

0xE0051038

10.4.9 GCTL_IOPOWER_INTR_MASK

I/O Power Change Interrupt Mask Register

Set to 1 to activate interrupt. Affects reporting of interrupts only, not logging.

13 USB_POWER_GOOD Set to 1 to report interrupt to CPU

12 VBUS_TH Set to 1 to report interrupt to CPU

11 VBAT Set to 1 to report interrupt to CPU

10 VBUS Set to 1 to report interrupt to CPU

9 USB25REG Set to 1 to report interrupt to CPU

8 USB33REG Set to 1 to report interrupt to CPU

7VIO5 Set to 1 to report interrupt to CPU

6 CVDDQ Set to 1 to report interrupt to CPU.

Note CVDDQ is required for chip operation (clock and reset). This interrupt will never trigger when it

is observable.

continued on next page

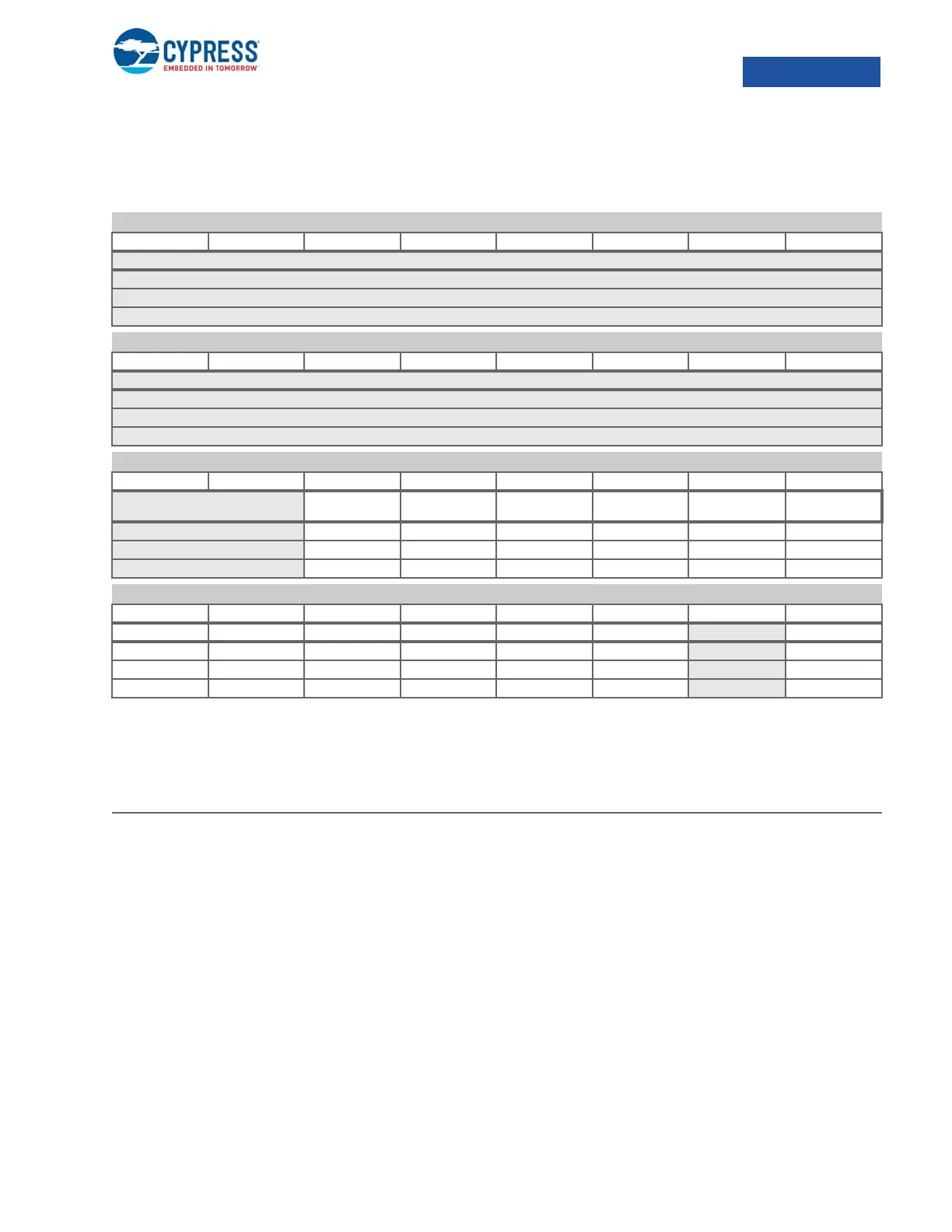

GCTL_IOPOWER_INTR_MASK I/O Power Change Interrupt Mask Register 0xE0051038

b31 b30 b29 b28 b27 b26 b25 b24

GCTL_IOPOWER_INTR_MASK I/O Power Change Interrupt Mask Register

b23 b22 b21 b20 b19 b18 b17 b16

GCTL_IOPOWER_INTR_MASK I/O Power Change Interrupt Mask Register

b15 b14 b13 b12 b11 b10 b9 b8

USB_POWER_

GOOD

VBUS_TH VBAT VBUS USB25REG USB33REG

R/W1C R/W1C R/W1C R/W1C R/W1C R/W1C

W1S W1S W1S W1S W1S W1S

0 0 0 0 0 0

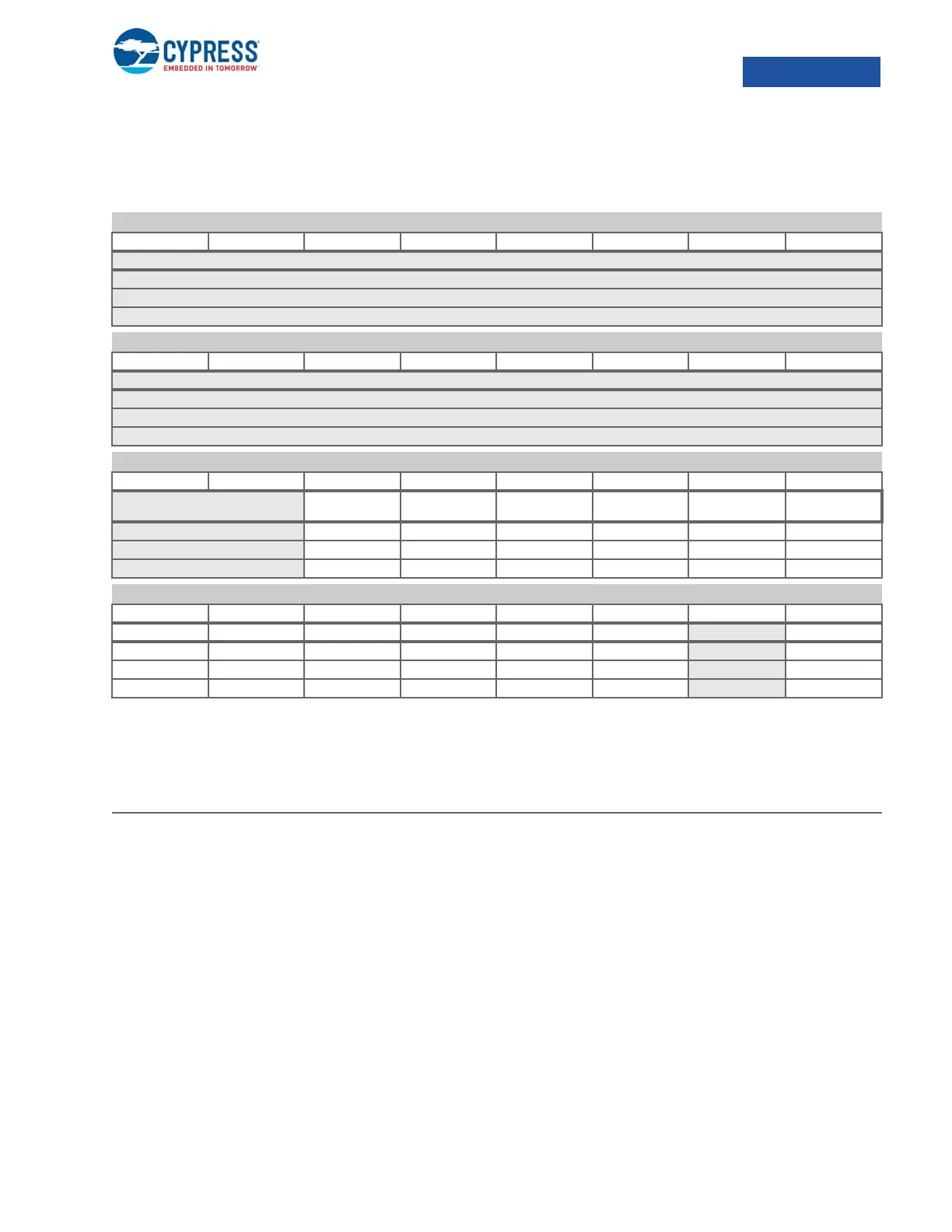

GCTL_IOPOWER_INTR_MASK I/O Power Change Interrupt Mask Register

b7 b6 b5 b4 b3 b2 b1 b0

VIO5 CVDDQ EFVDDQ VIO4 VIO3 VIO2 VIO1

R/W1C R/W1C R/W1C R/W1C R/W1C R/W1C R/W1C

W1S W1S W1S W1S W1S W1S W1S

0 0 0 0 0 0 0

Bit Name Description

Loading...

Loading...