EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 364

PP_DRQR5_MASK

0xE0017E20

10.8.5 PP_DRQR5_MASK

P-Port DRQ/R5 Mask Register

These registers have the same layout as PP_EVENT and mask which events lead to assertion of INTR or DRQ/R5 respec-

tively. DRQR5 is a signal that can be put on any GPIF CTRL[x] line (see GPIF_BUS_SELECT) and R5 is an MMC event noti-

fication protocol relevant only in PMMC mode.

15 WAKEUP 1 Forward EVENT onto DRQ line

14 WR_MB_EMPTY 1 Forward EVENT onto DRQ line

13 RD_MB_FULL 1 Forward EVENT onto DRQ line

12 DMA_READY_EV 1 Forward EVENT onto DRQ line

11 DMA_WMARK_EV 1 Forward EVENT onto DRQ line

7GPIF_ERR 1 Forward EVENT onto DRQ line

5PIB_ERR 1 Forward EVENT onto DRQ line

4GPIF_INT 1 Forward EVENT onto DRQ line

3 SOCK_AGG_BH 1 Forward EVENT onto DRQ line

2 SOCK_AGG_BL 1 Forward EVENT onto DRQ line

1 SOCK_AGG_AH 1 Forward EVENT onto DRQ line

0 SOCK_AGG_AL 1 Forward EVENT onto DRQ line

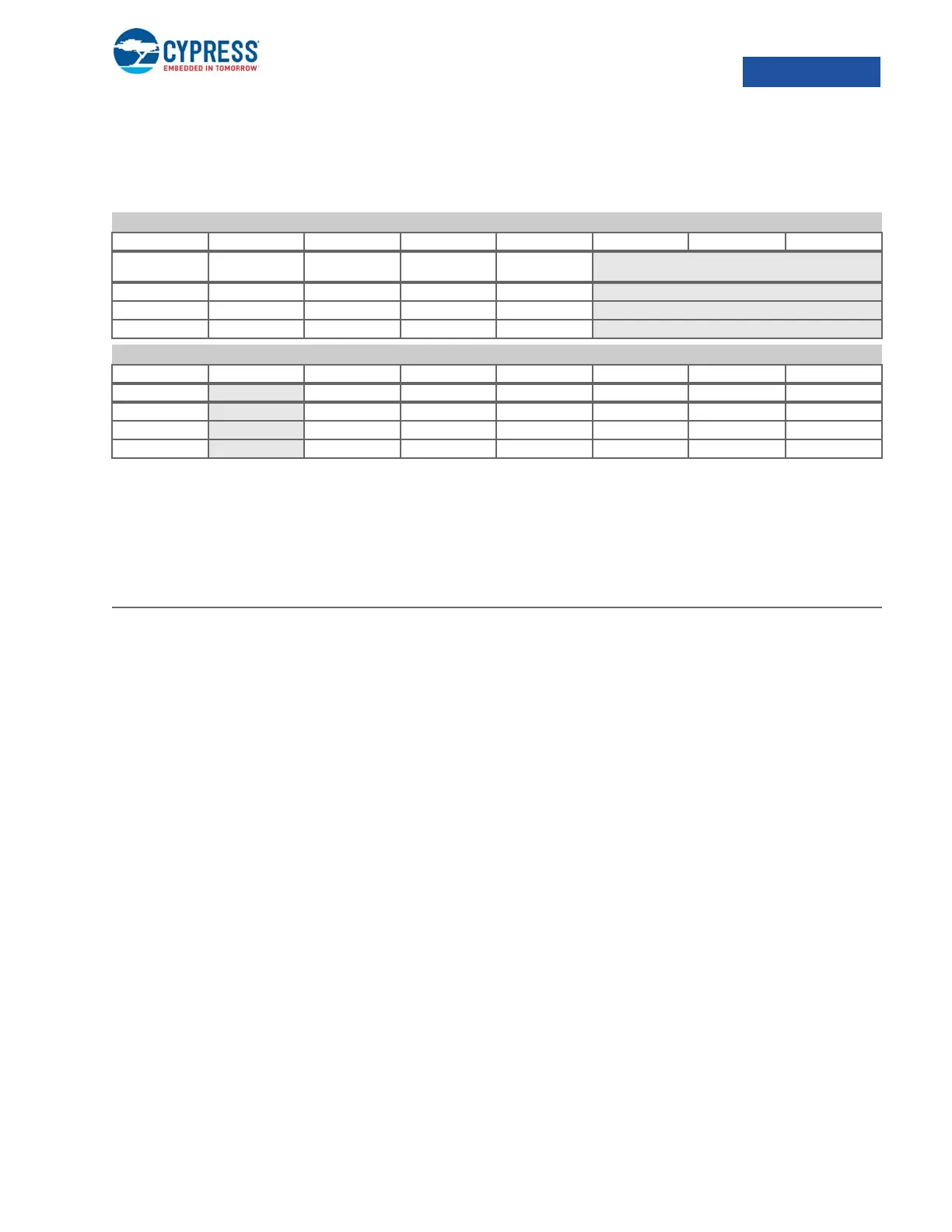

PP_DRQR5_MASK P-Port DRQ/R5 Mask Register 0xE0017E20

b15 b14 b13 b12 b11 b10 b9 b8

WAKEUP WR_MB_EMPTY RD_MB_FULL DMA_READY_EV

DMA_WMARK_

EV

R/W R/W R/W R/W R/W

RRRRR

00100

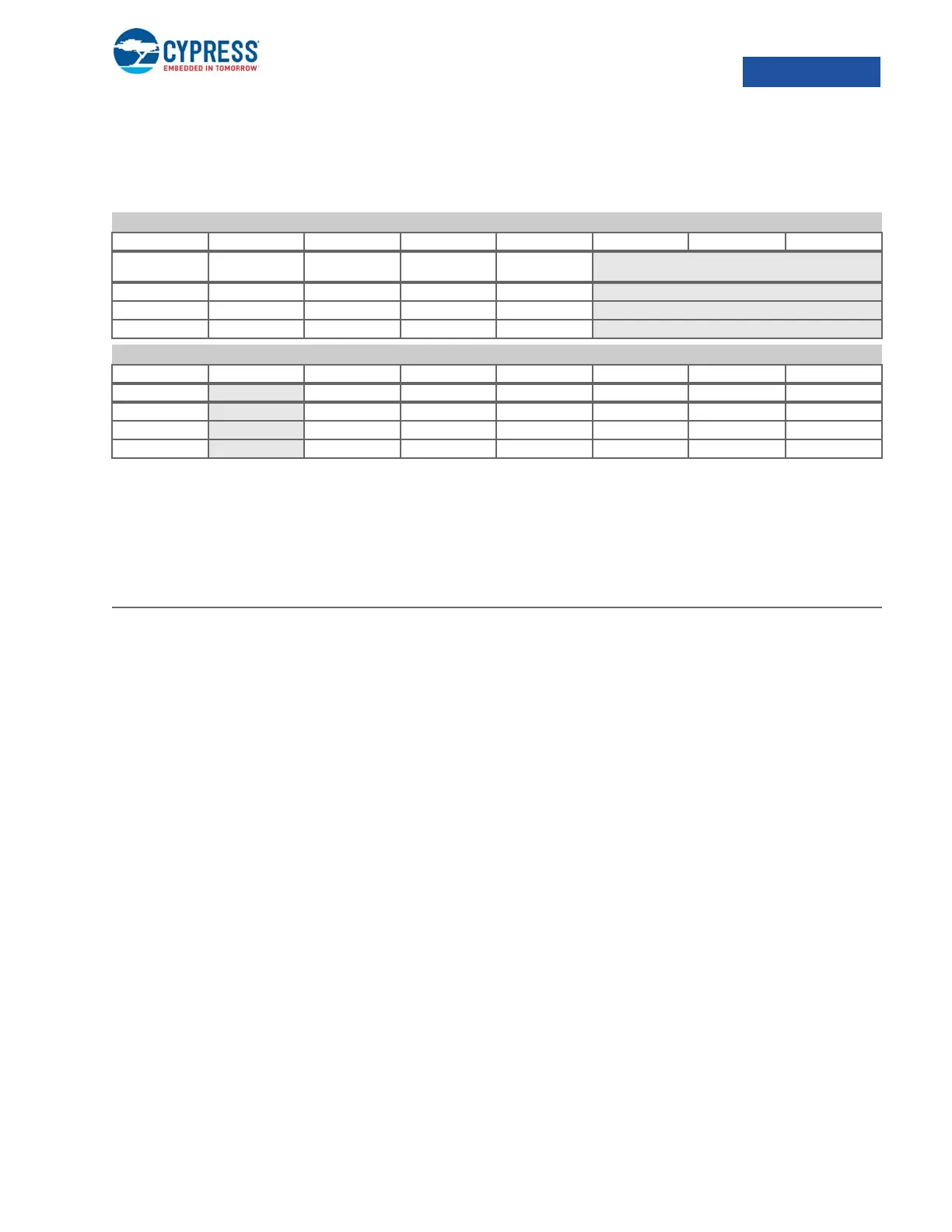

PP_DRQR5_MASK P-Port DRQ/R5 Mask Register

b7 b6 b5 b4 b3 b2 b1 b0

GPIF_ERR PIB_ERR GPIF_INT SOCK_AGG_BH SOCK_AGG_BL SOCK_AGG_AH SOCK_AGG_AL

R/W R/W R/W R/W R/W R/W R/W

R

RRRRRR

0

000000

Bit Name Description

Loading...

Loading...