EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 76

FX3 DMA Subsystem

s->status &= ~(CY_U3P_LPP_GO_ENABLE | CY_U3P_LPP_WRAPUP);

s->intr = 0xFF;

while (s->status & CY_U3P_LPP_ENABLED)

__nop ();

/* Flush EP0-IN as well. */

UIB->eepm_endpoint[0] |= CY_U3P_UIB_SOCKET_FLUSH;

CyFx3BootBusyWait (10);

UIB->eepm_endpoint[0] &= ~CY_U3P_UIB_SOCKET_FLUSH;

status = CY_FX3_BOOT_ERROR_ABORTED;

break;

}

} while (timeout > 0);

return status;

}

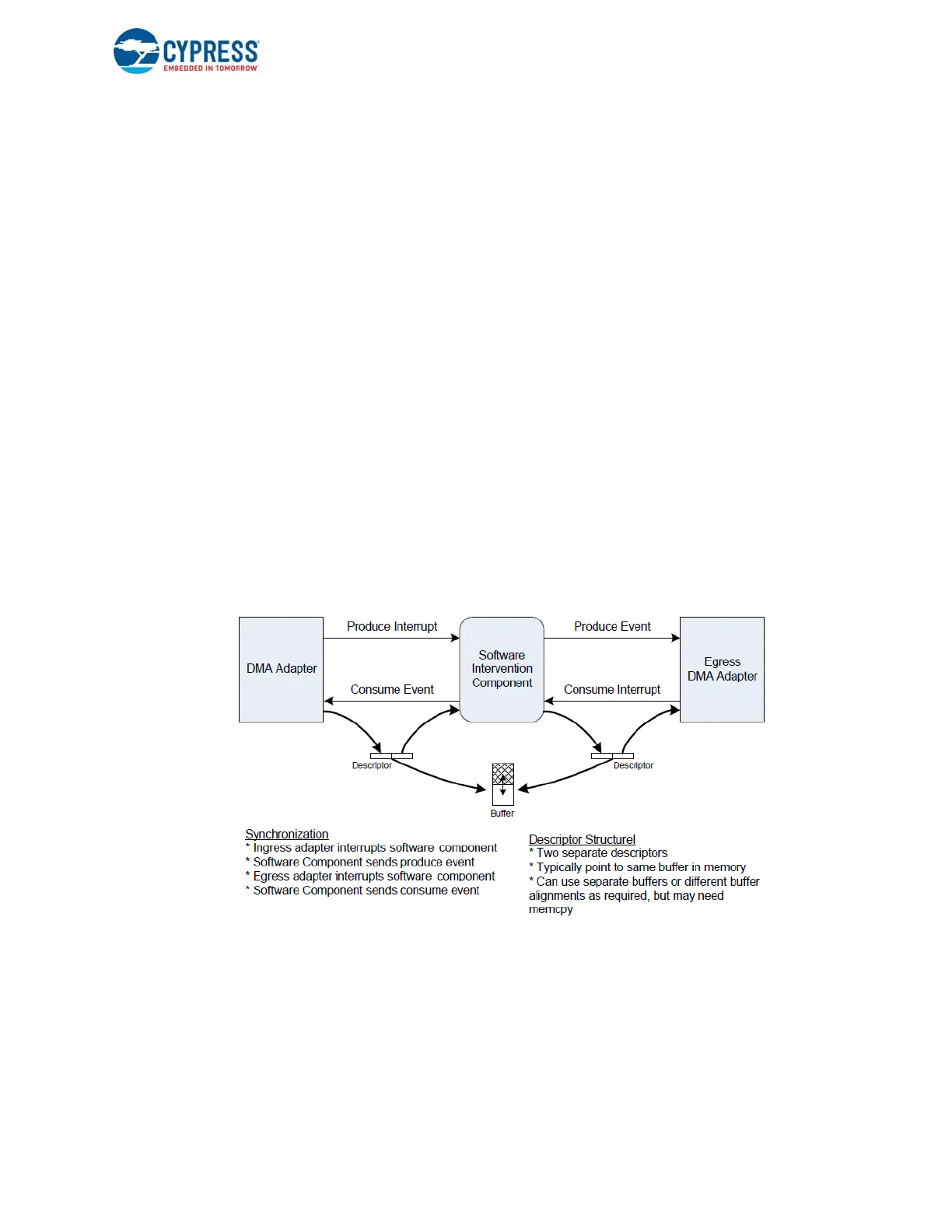

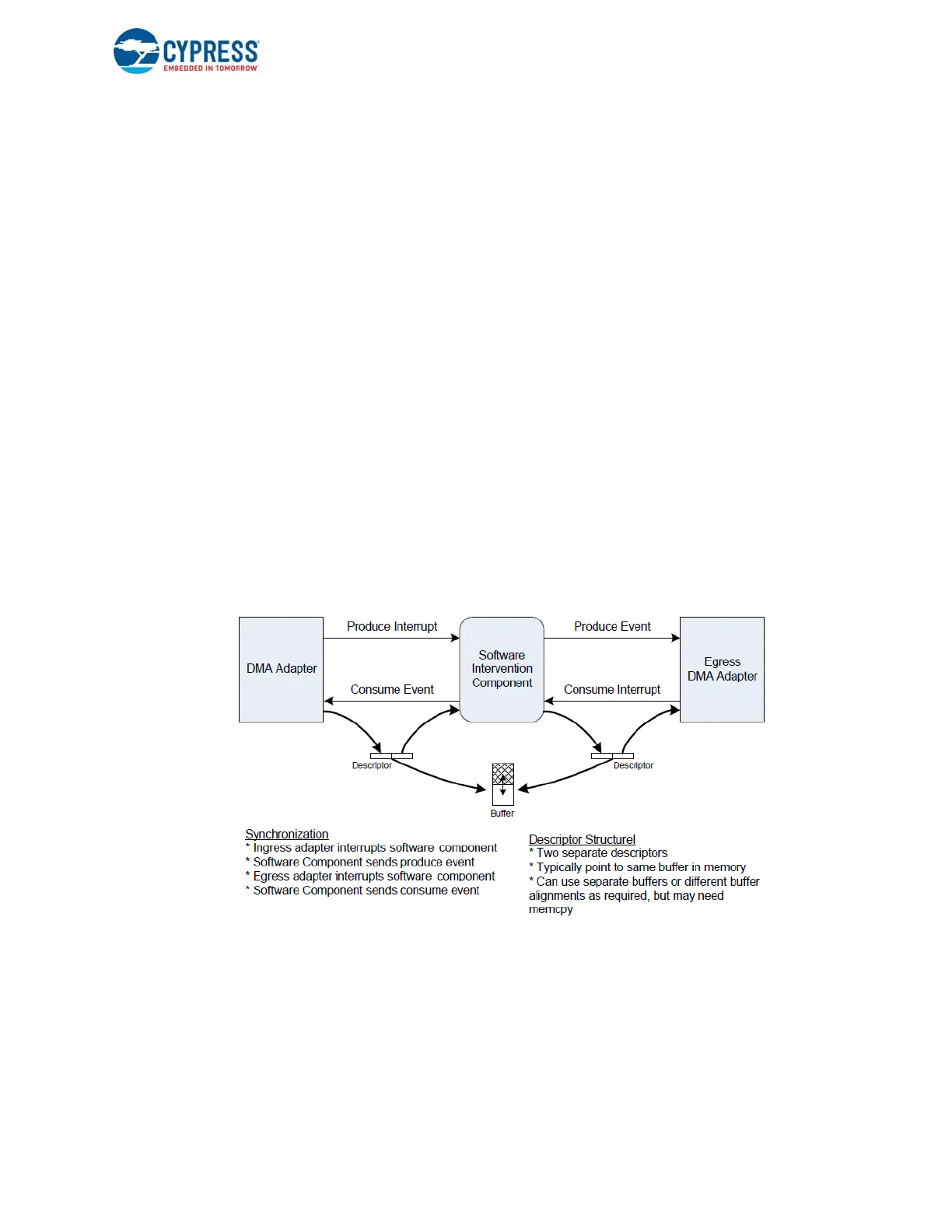

5.7 CPU Intervention In Between Ingress and Egress

Although it is rarely needed, it is possible to interpose a CPU intervention in between an ingress and egress DMA adapter.

Conceptually, this means the CPU (the software component) acts as the consumer agent to the producing (ingress) adapter

and acts as the producer agent to the consuming (egress) adapter. This model is depicted in Figure 5-12.

Figure 5-12. CPU Intervention in DMA Transfer Path

This mode will have a significant negative performance impact on high-bandwidth transfers because the CPU gets into the

critical path of every buffer transferred. This mode should only be used to handle special case stream requirements or to

implement processing of the actual data by the CPU such as DSP applications.

Loading...

Loading...