EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 655

SDMMC_NCR

0xFC

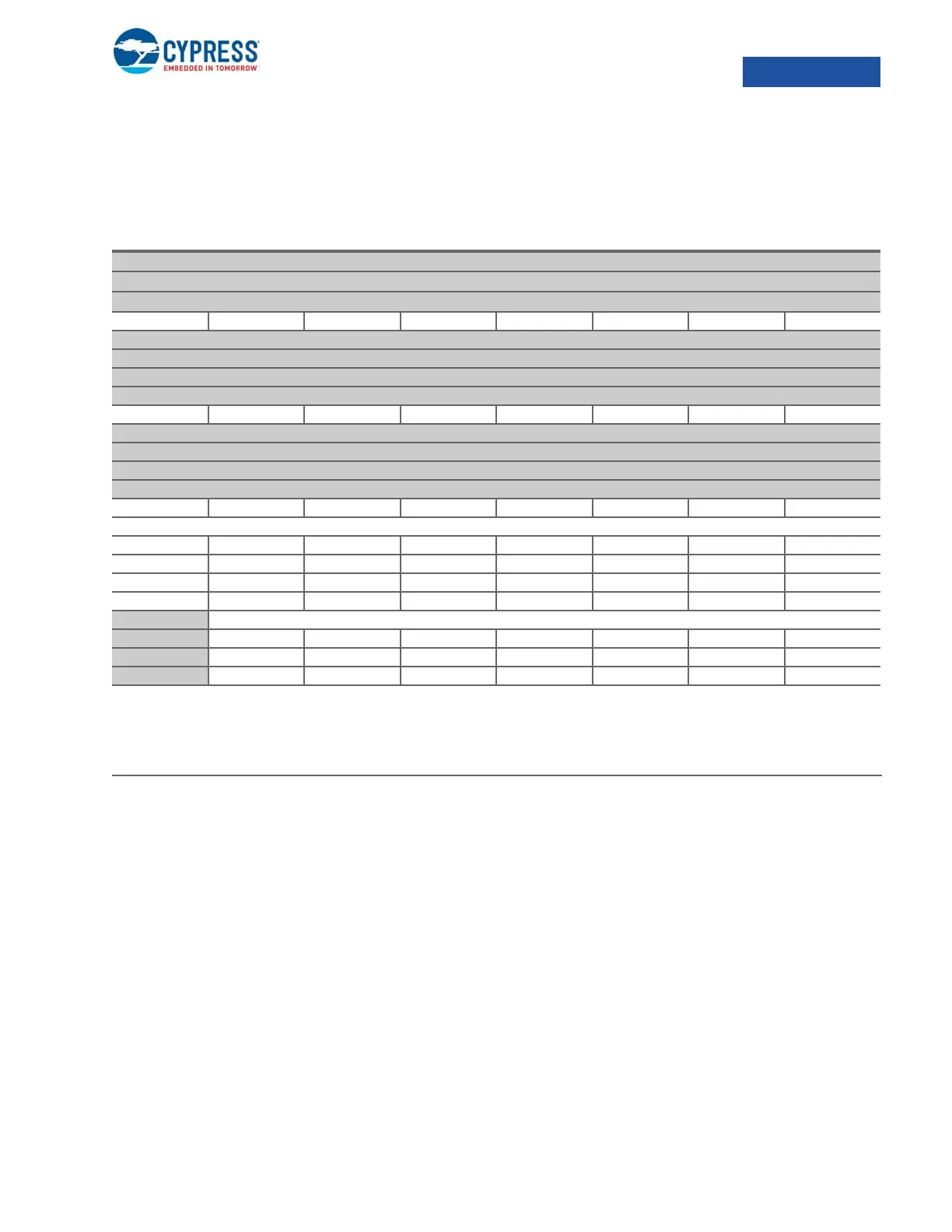

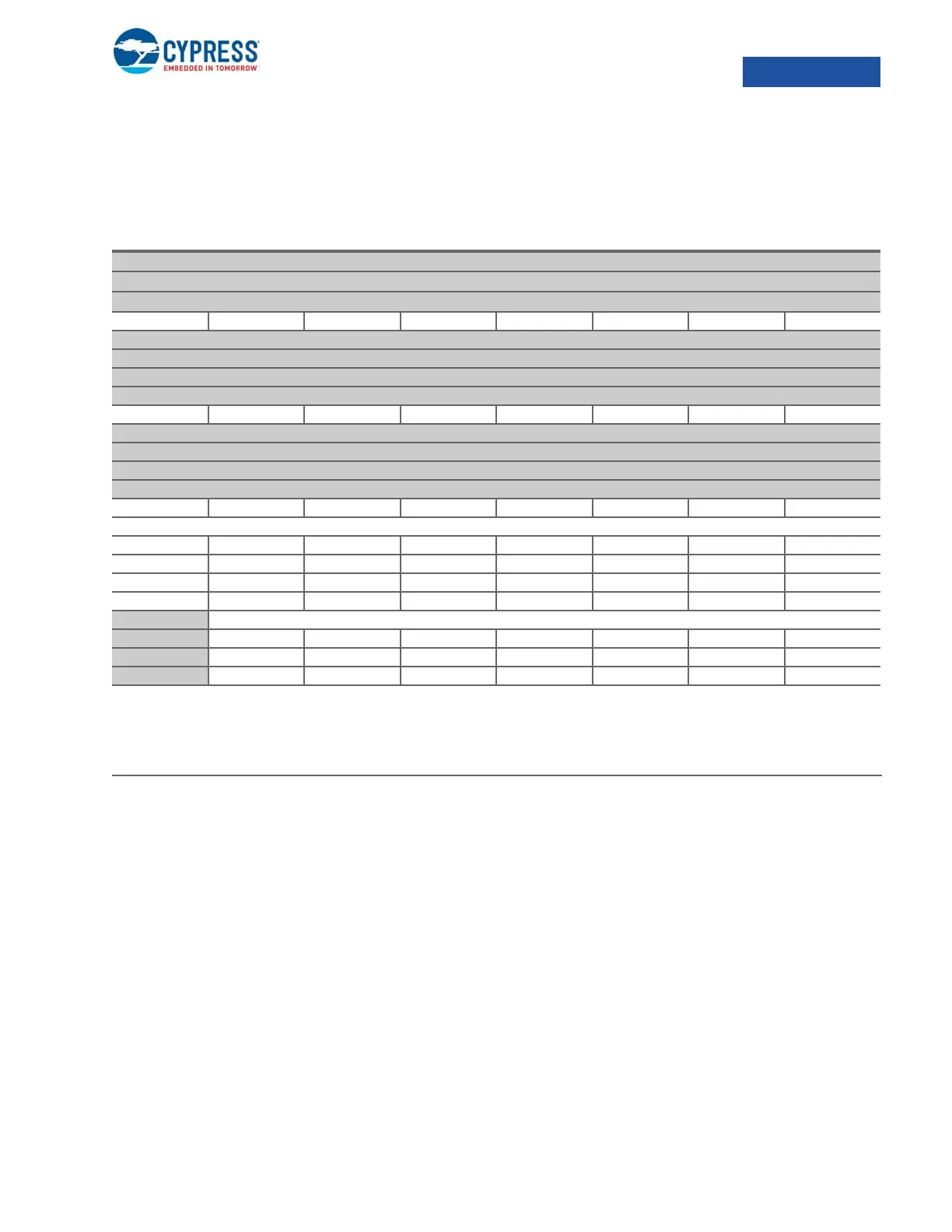

10.26.23 SDMMC_NCR

SDMMC Command Response Timing Register #1

This register controls timing between command and response. There are two copies of this register corresponding to the two

storage ports. The address of each register is calculated as 0xe0020048 + (port * 0x0400).

15:8 NRC_MIN Specifies the minimum separation in clock cycles between the end bit of a response and the start bit

of the next command.

6:0 NCR_MAX Specifies the timeout period for which the SIB will wait to receive a response, in terms of number of

cycles from end bit of command.

SDMMC_NCR

SDMMC Command Response Timing Register #1

0xE0020048

b31 b30 b29 b28 b27 b26 b25 b24

b23 b22 b21 b20 b19 b18 b17 b16

b15 b14 b13 b12 b11 b10 b9 b8

NRC_MIN[7:0]

RRRRRRRR

R/W R/W R/W R/W R/W R/W R/W R/W

00001000

b7 b6 b5 b4 b3 b2 b1 b0

NCR_MAX[6:0]

RRRRRRR

R/W R/W R/W R/W R/W R/W R/W

1000111

Bit Name Description

Loading...

Loading...