EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 341

GPIF_THREAD_CONFIG

0xE00140FC

10.7.35 GPIF_THREAD_CONFIG

Thread Configuration Register

There are four GPIF_THREAD_CONFIG registers. The address of each is calculated as GPIF_THREAD_CONFIG(x) = 0xE-

00140FC + (x*0x4). Hence GPIF_THREAD_CONFIG(0) is at address 0xE00140FC, GPIF_THREAD_CONFIG(1) is at

address 0xE00140FC + 0x4 and so on. The definition of each of these is the same.

Configures the active socket and thread watermark. (All sockets behind the thread share the watermark). The hardware gets

the status and direction of the sockets from the adapter.The watermark signal is the limit hit indicator of a counter that counts

read/write accesses that happen on the interface. The limit of this counter is programmed by the hardware to “end of usable

space” and is reset to 0 by PIB hardware as dma_ready (available flag) goes from 0->1.

31 ENABLE Enables the thread controller for operation. Can be set by firmware after initializing THREAD_SOCK

and other fields. Will be set by hardware when THREAD_SOCK is written to by hardware.

29:16 WATERMARK[13:0] Watermark position. Indicates number words that would be subtracted from the end of usable space/

data. Watermark needs to be programmed to a value greater than the round trip flag latency of the

system.

This latency is a sum of three quantities namely (1) FX3 latency between seeing the end of the last

burst that completely fills the buffer to the time the full/empty flag updates (can be calculated from

generic gpif params), (2). Expected time of arrival of a flow control signal that would prevent the AP

from issuing the next burst (as measured from the end of the burst) (3). Any additional group latency

between the APs dma controller logic and the interface pins in both directions.

continued on next page

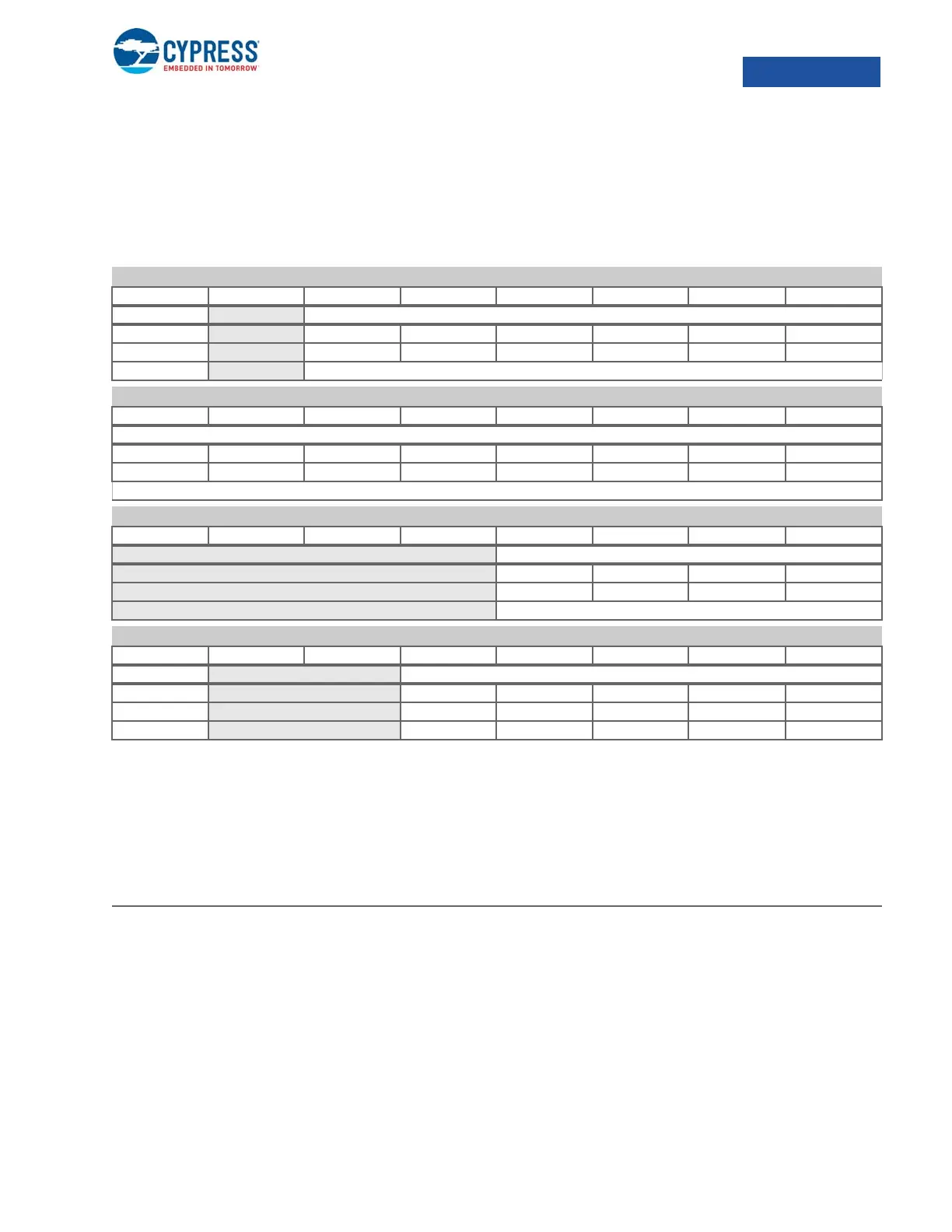

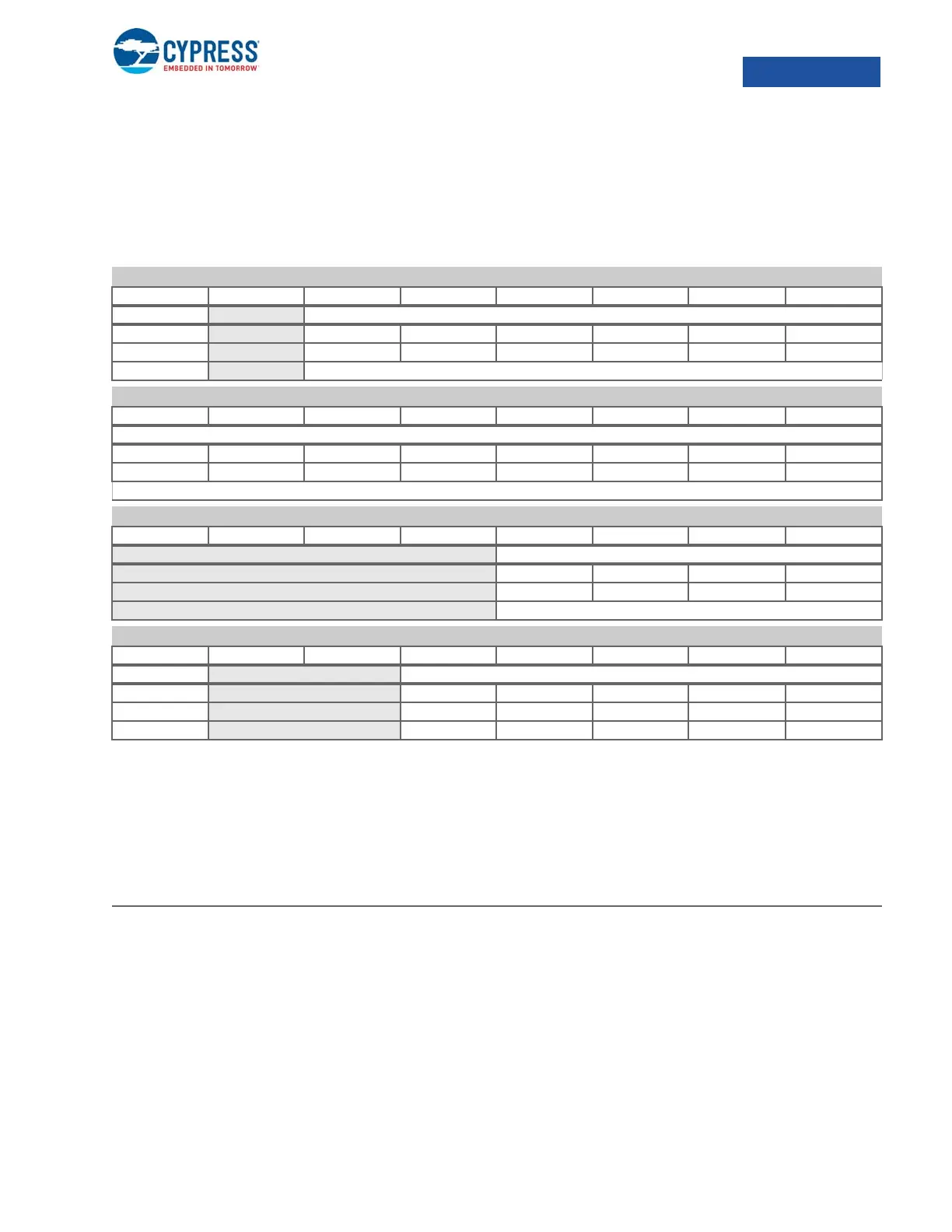

GPIF_THREAD_CONFIG Thread Configuration Register 0xE00140FC

b31 b30 b29 b28 b27 b26 b25 b24

ENABLE WATERMARK[13:8]

R/W R/W R/W R/W R/W R/W R/W

R/W

RRRRRR

0

GPIF_THREAD_CONFIG Thread Configuration Register

b23 b22 b21 b20 b19 b18 b17 b16

WATERMARK[7:0]

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

1

GPIF_THREAD_CONFIG Thread Configuration Register

b15 b14 b13 b12 b11 b10 b9 b8

BURST_SIZE[3:0]

R/W R/W R/W R/W

RRRR

4

GPIF_THREAD_CONFIG Thread Configuration Register

b7 b6 b5 b4 b3 b2 b1 b0

WM_CFG THREAD_SOCK[4:0]

R/W R/W R/W R/W R/W R/W

R

R/W R/W R/W R/W R/W

0

01010

Bit Name Description

Loading...

Loading...