EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 563

UART_CONFIG

0xE0000800

10.20 UART Registers

10.20.1 UART_CONFIG

UART Configuration and Mode Register

Various modes of the UART block.

31 ENABLE Enable block here, but only after all the configuration is set. Do not set this bit to 1 while changing any

other value in this register. This bit will be synchronized to the core clock.

Setting this bit to 0 will complete transmission of current sample. When DMA_MODE=1 any remain-

ing samples in the pipeline are discarded. When DMA_MODE=0 no samples are lost.

30 TX_CLEAR Use only when ENABLE=0; behavior undefined when ENABLE=1

0 Do nothing

1 Clear transmit FIFO

(After TX_CLEAR is set, software must wait for TX_DONE before clearing it)

29 RX_CLEAR 0 Do nothing

1 Clear receive FIFO

(Software must wait for RX_DATA=0 before clearing this bit again)

continued on next page

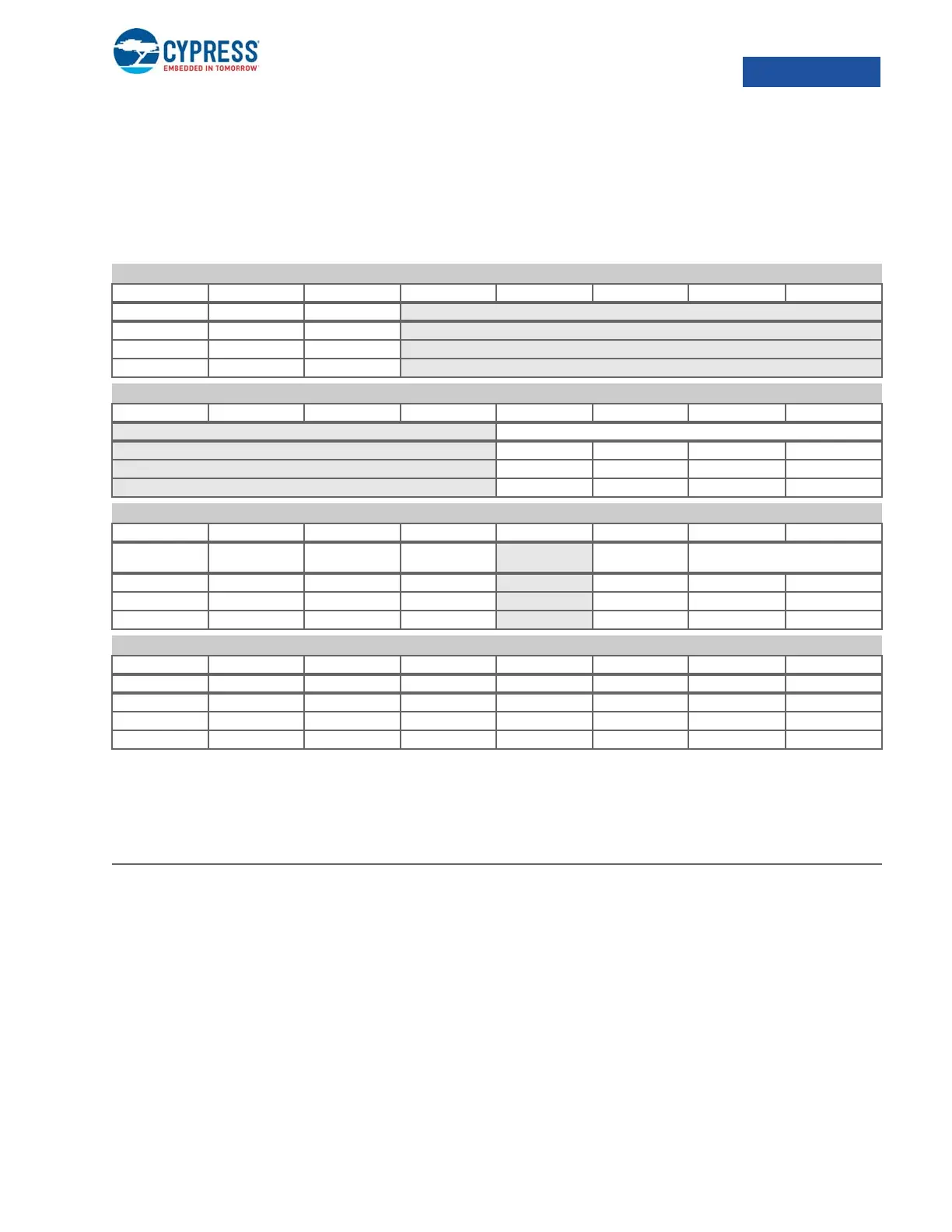

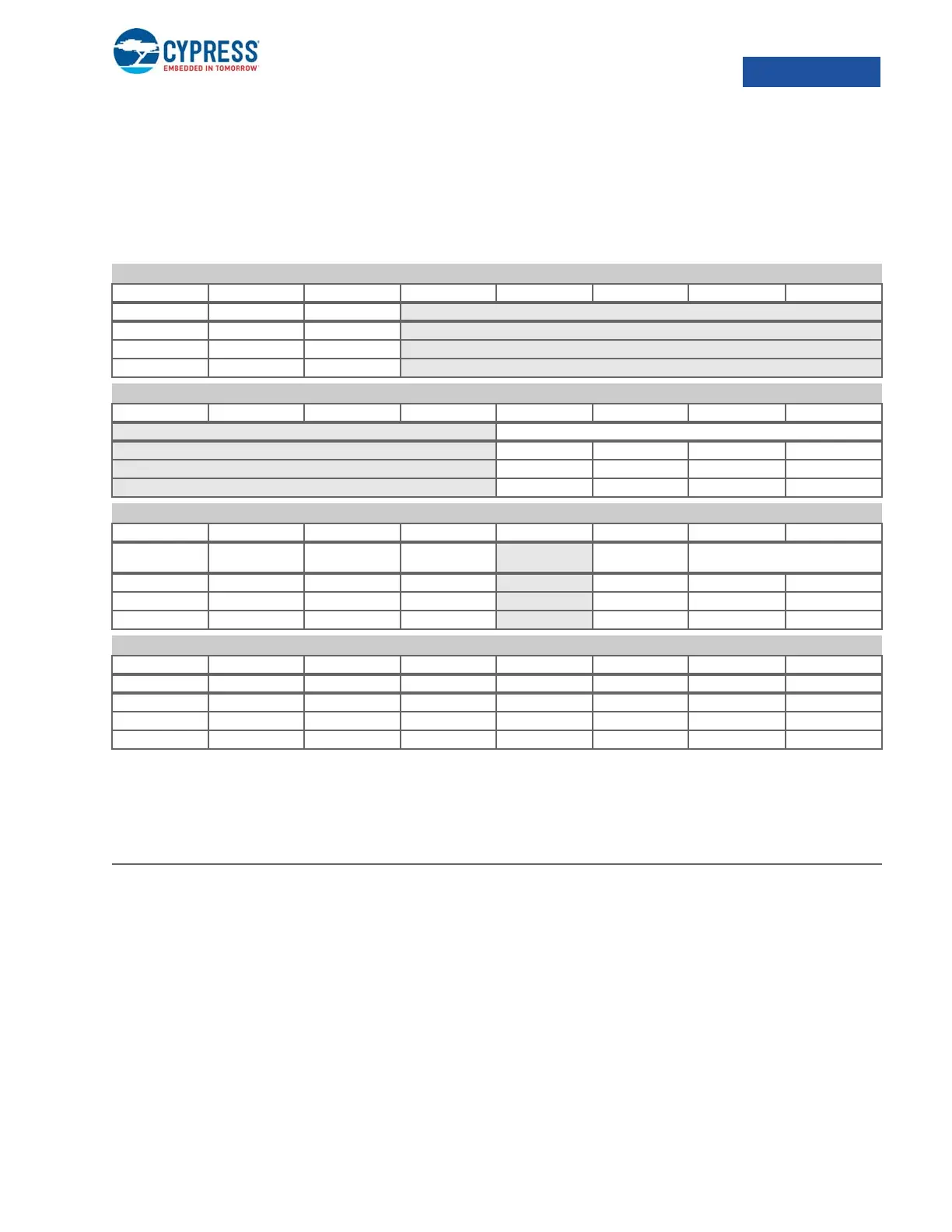

UART_CONFIG UART Configuration and Mode Register 0xE0000800

b31 b30 b29 b28 b27 b26 b25 b24

ENABLE TX_CLEAR RX_CLEAR

R/W R/W R/W

RRR

000

UART_CONFIG UART Configuration and Mode Register

b23 b22 b21 b20 b19 b18 b17 b16

RX_POLL[3:0]

R/W R/W R/W R/W

RRRR

0000

UART_CONFIG UART Configuration and Mode Register

b15 b14 b13 b12 b11 b10 b9 b8

TX_BREAK

RX_FLOW_CTRL

_ENBL

TX_FLOW_CTRL

_ENBL

RTS DMA_MODE STOP_BITS[1:0]

R/W R/W R/W R/W R/W R/W R/W

RRRR

RRR

0001

000

UART_CONFIG UART Configuration and Mode Register

b7 b6 b5 b4 b3 b2 b1 b0

RX_STICKY_BIT TX_STICKY_BIT PARITY_STICKY PARITY_ODD PARITY LOOP_BACK TX_ENABLE RX_ENABLE

R/W R/W R/W R/W R/W R/W R/W R/W

RRRRRRRR

00000010

Bit Name Description

Loading...

Loading...