EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 251

GCTL_IOPOWER

0xE0051030

10.4.7 GCTL_IOPOWER

I/O Power Observability Register

This register can be used to detect I/O Power status on various I/O domains

21 REG_BYPASS_EN Controls the 3.3-V active regulator's bypass mode. This mode enables an external voltage

to be applied to the internal 3.3-V node by bypassing the 3.3-V regulator. It allows the 2.5-V

regulator to be tested and characterized across a different range of input supply voltages

rather than from a single regulated 3.3-V supply. This bit has no function when the regulator

is in standby mode.

0 3.3-V active regulator is not in bypass mode

1 3.3-V active regulator is in bypass mode

20 REG_CARKIT_EN Enables the regulator to provide different output voltage from the 3.3-V regulator. Output

value is selected by the reg_carkit_sel[1:0] bits.

1 Enables regulator to output different voltages for the carkit mode. NOT ALLOWED

for chip-level carkit UART mode because the regulator 2.5-V supply output is dis-

abled, which is not supported by the USB2.0 PHY.

0 Regulator operates normally.

continued on next page

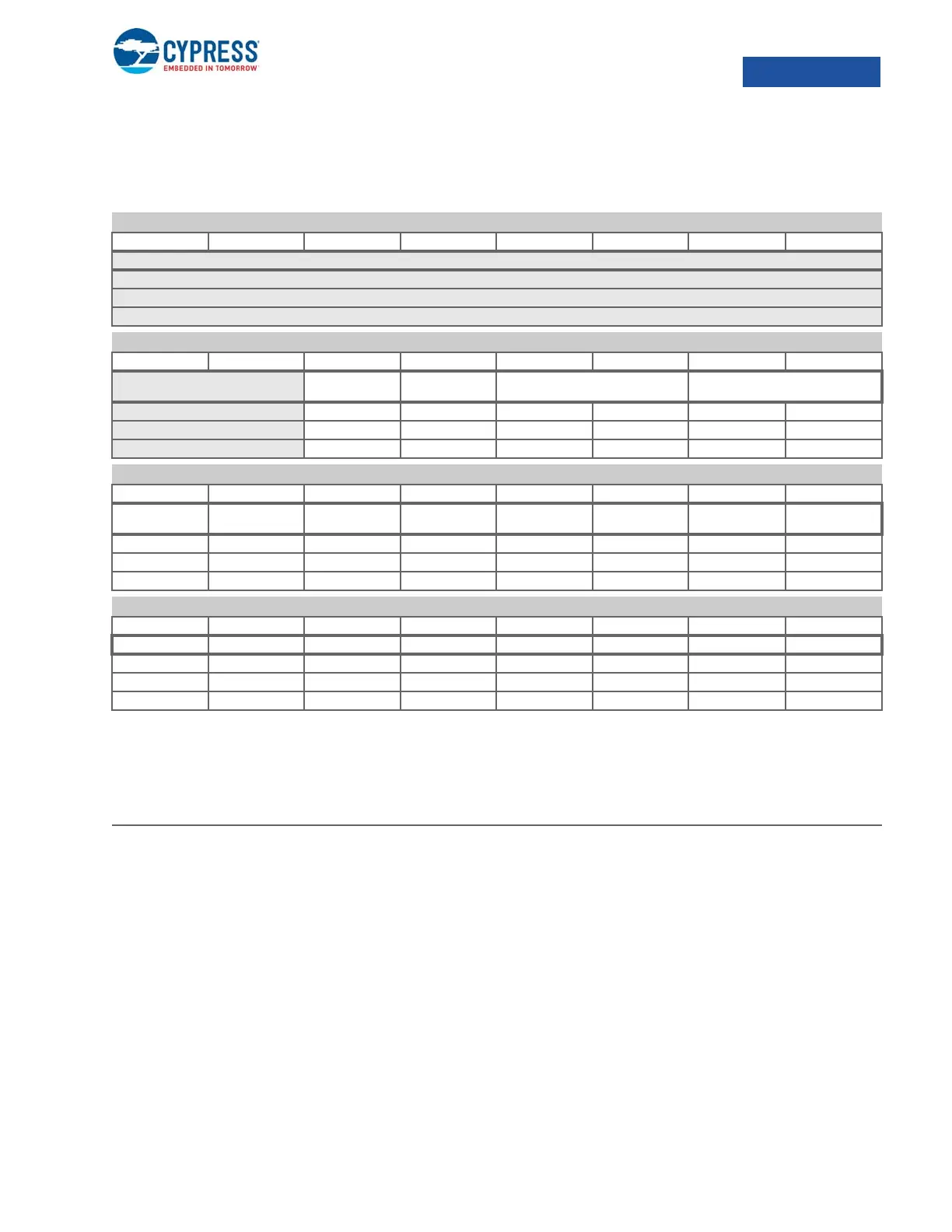

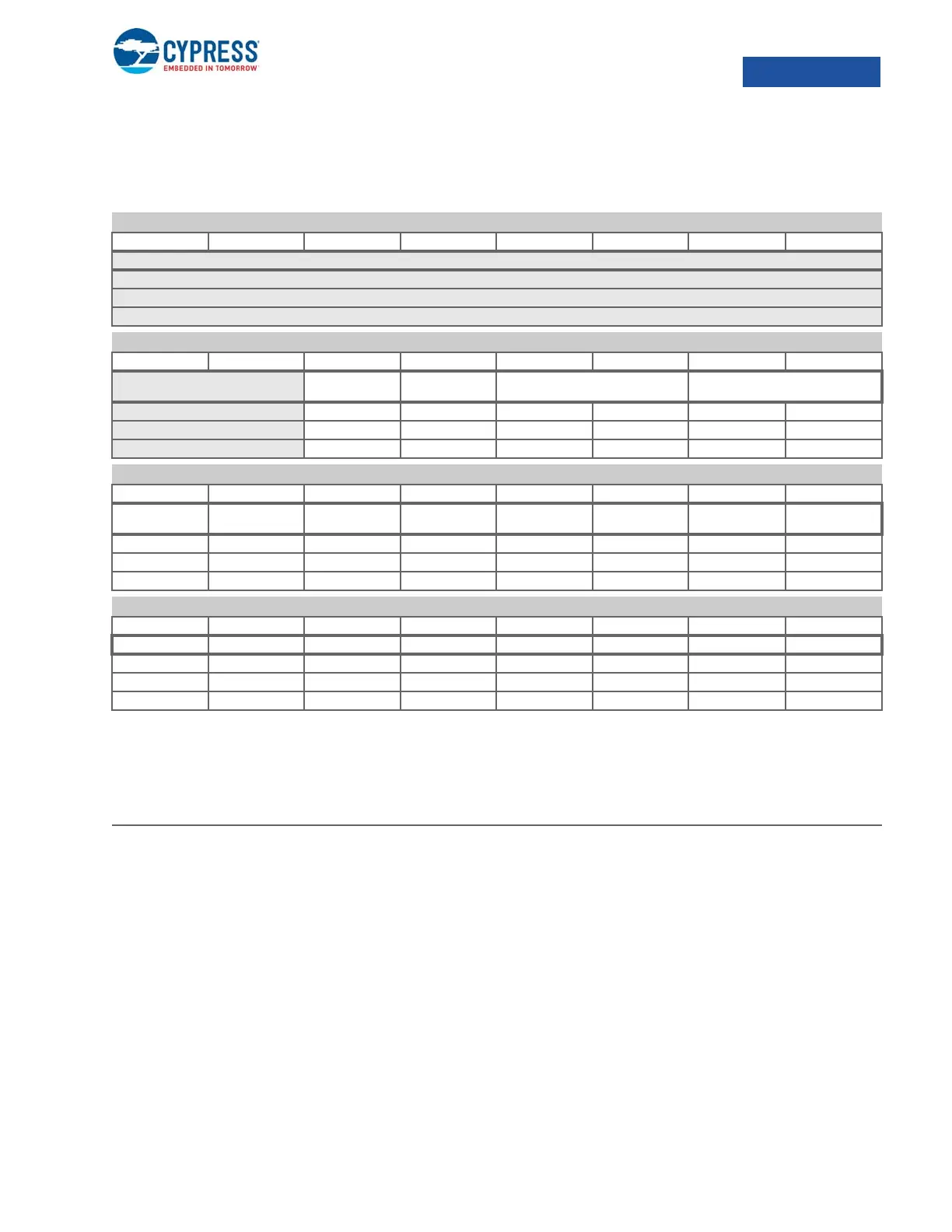

GCTL_IOPOWER I/O Power Observability Register 0xE0051030

b31 b30 b29 b28 b27 b26 b25 b24

GCTL_IOPOWER I/O Power Observability Register

b23 b22 b21 b20 b19 b18 b17 b16

REG_BYPASS_

EN

REG_CARKIT_EN REG_CARKIT_SEL[1:0] USB_REGULATOR_TRIM[1:0]

R/W R/W R/W R/W R/W R/W

RRRRRR

000000

GCTL_IOPOWER I/O Power Observability Register

b15 b14 b13 b12 b11 b10 b9 b8

00

USB_POWER_

GOOD

VBUS_TH PDS_G[1:0] VBUS USB25REG USB33REG

RRRRRRRR

R R R/W R/W R/W R/W R/W R/W

00XXXXXX

GCTL_IOPOWER I/O Power Observability Register

b7 b6 b5 b4 b3 b2 b1 b0

VIO5 CVDDQ EFVDDQ VIO4 VIO3 VIO2 0 VIO1

RRRRRRRR

R/W R/W R/W R/W R/W R/W R R/W

XXXXXX0 X

Bit Name Description

Loading...

Loading...