EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 531

I2S_STATUS

0xE0000004

10.18.2 I2S_STATUS

I2S Status Register

Status and error register. Most status bits are used to generate an interrupt on positive edge into INTR register.

28 BUSY Indicates the block is busy transmitting data. This field may remain asserted after the block is sus-

pended and must be polled before changing any configuration values.

27:24 ERROR_CODE[3:0] Error code, only relevant when ERROR=1. ERROR logs only the FIRST error to occur and will never

change value as long as ERROR=1.

11 Left TX FIFO/DMA socket underflow

12 Right TX FIFO/DMA socket underflow

13 Write to left TX FIFO when FIFO full

14 Write to right TX FIFO when FIFO full

15 No error

8 ERROR An internal error has occurred with cause ERROR_CODE. Must be cleared by software. Sticky

7 NO_DATA No data is currently available for output, but socket does not indicate empty. Only relevant when

DMA_MODE=1. Non sticky.

6 PAUSED Output is paused (PAUSE has taken effect). Non sticky

continued on next page

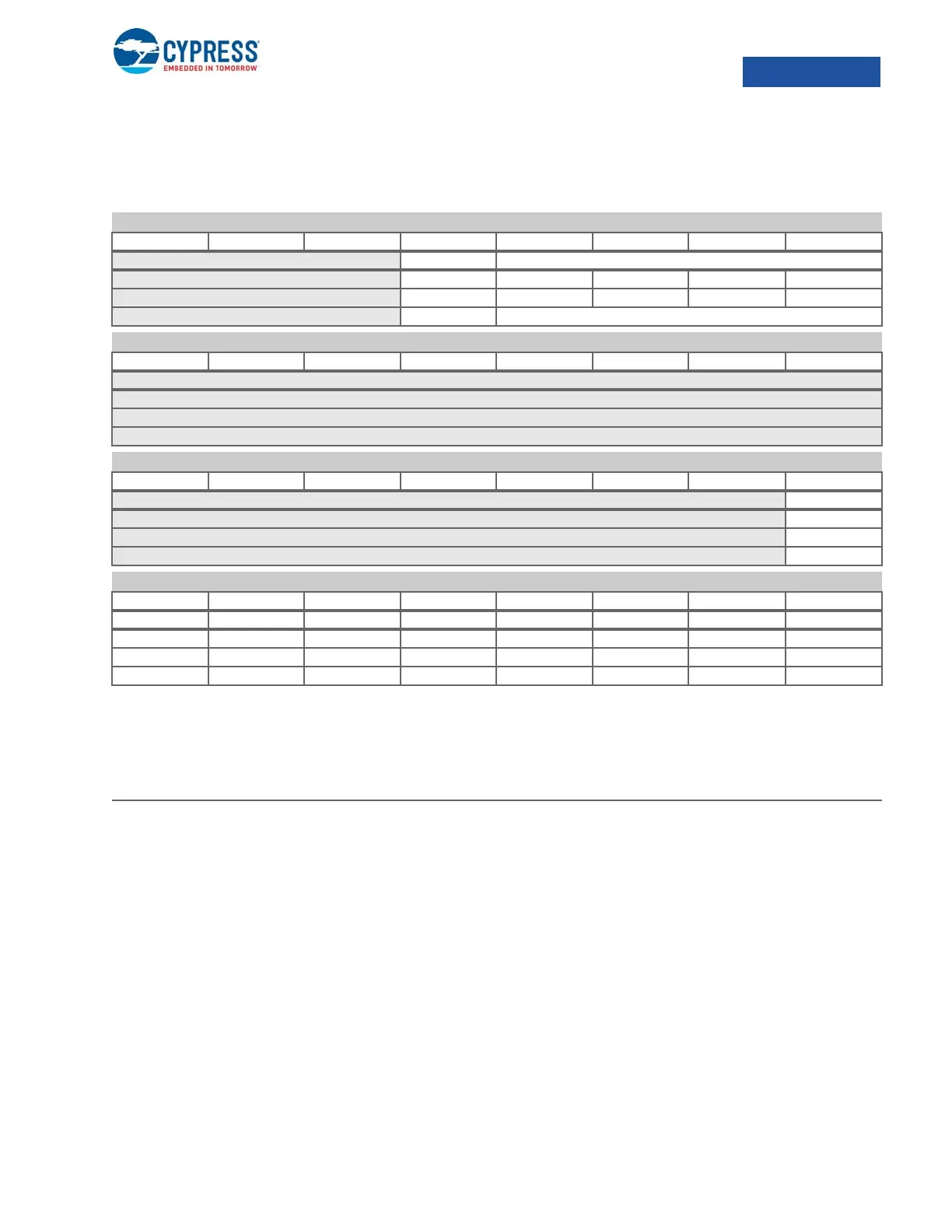

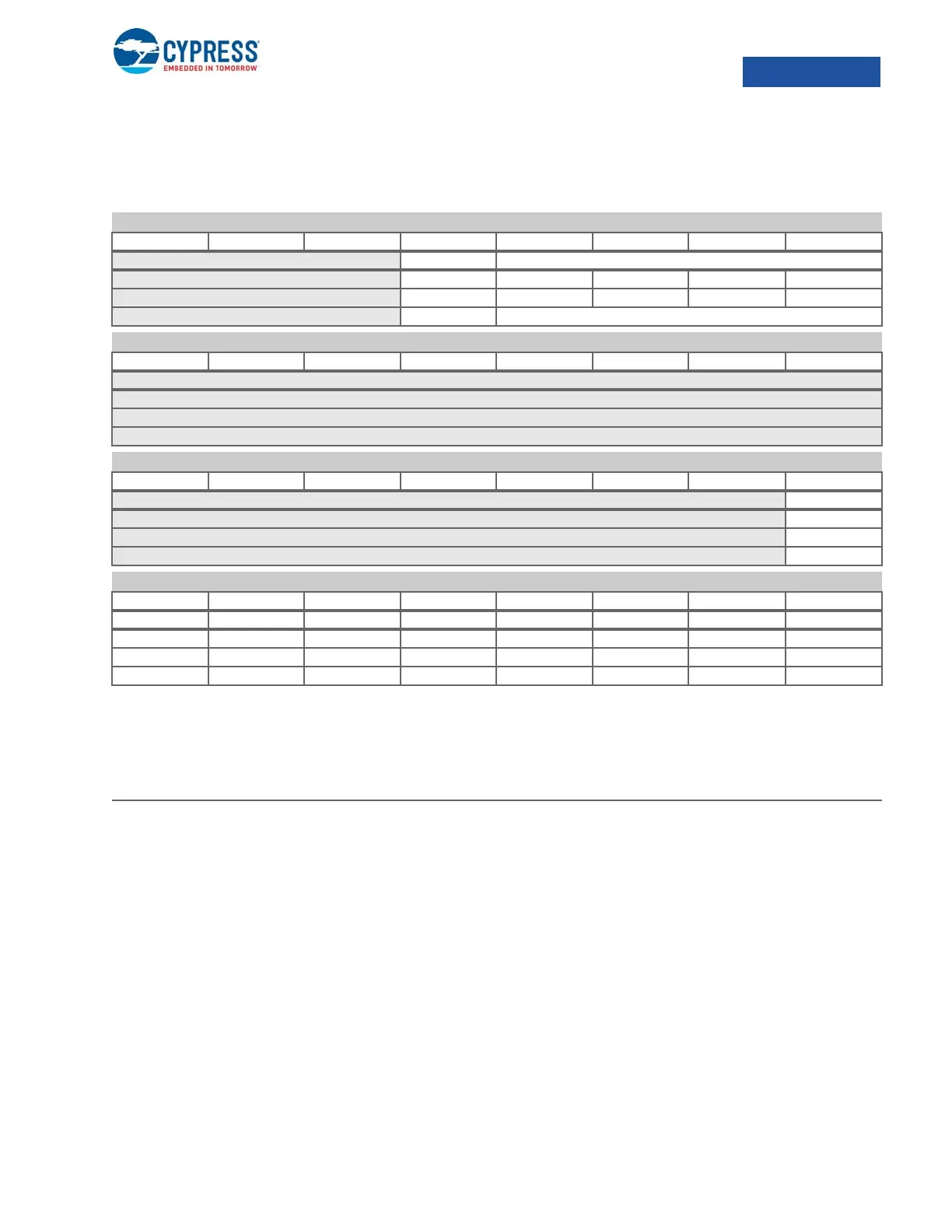

I2S_STATUS I2S Status Register 0xE0000004

b31 b30 b29 b28 b27 b26 b25 b24

BUSY ERROR_CODE[3:0]

RRRRR

WWWWW

00xF

I2S_STATUS I2S Status Register

b23 b22 b21 b20 b19 b18 b17 b16

I2S_STATUS I2S Status Register

b15 b14 b13 b12 b11 b10 b9 b8

ERROR

R/W1C

R/W1S

0

I2S_STATUS I2S Status Register

b7 b6 b5 b4 b3 b2 b1 b0

NO_DATA PAUSED TXR_HALF TXR_SPACE TXR_DONE TXL_HALF TXL_SPACE TXL_DONE

RRRRRRRR

WWWWWWWW

00110110

Bit Name Description

Loading...

Loading...