EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 659

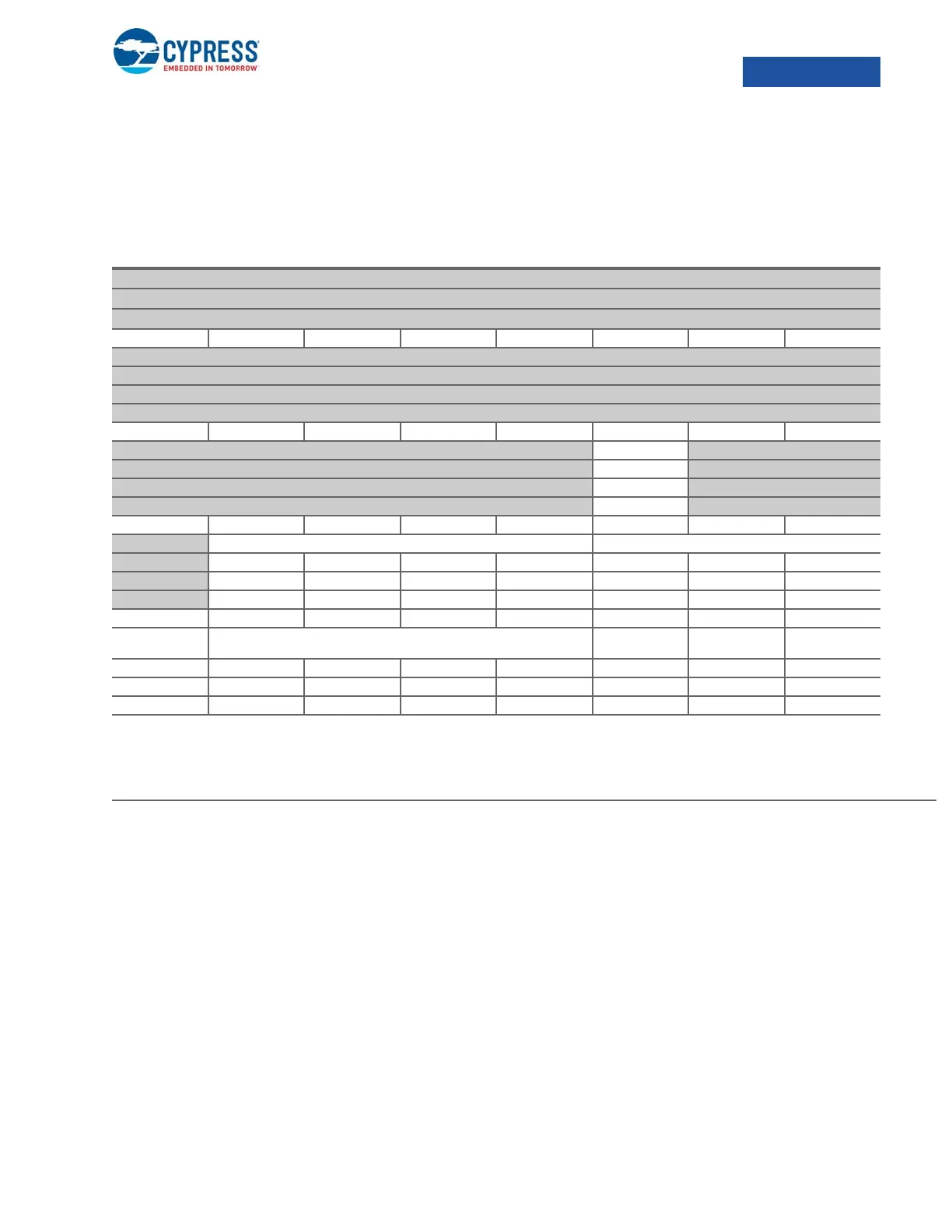

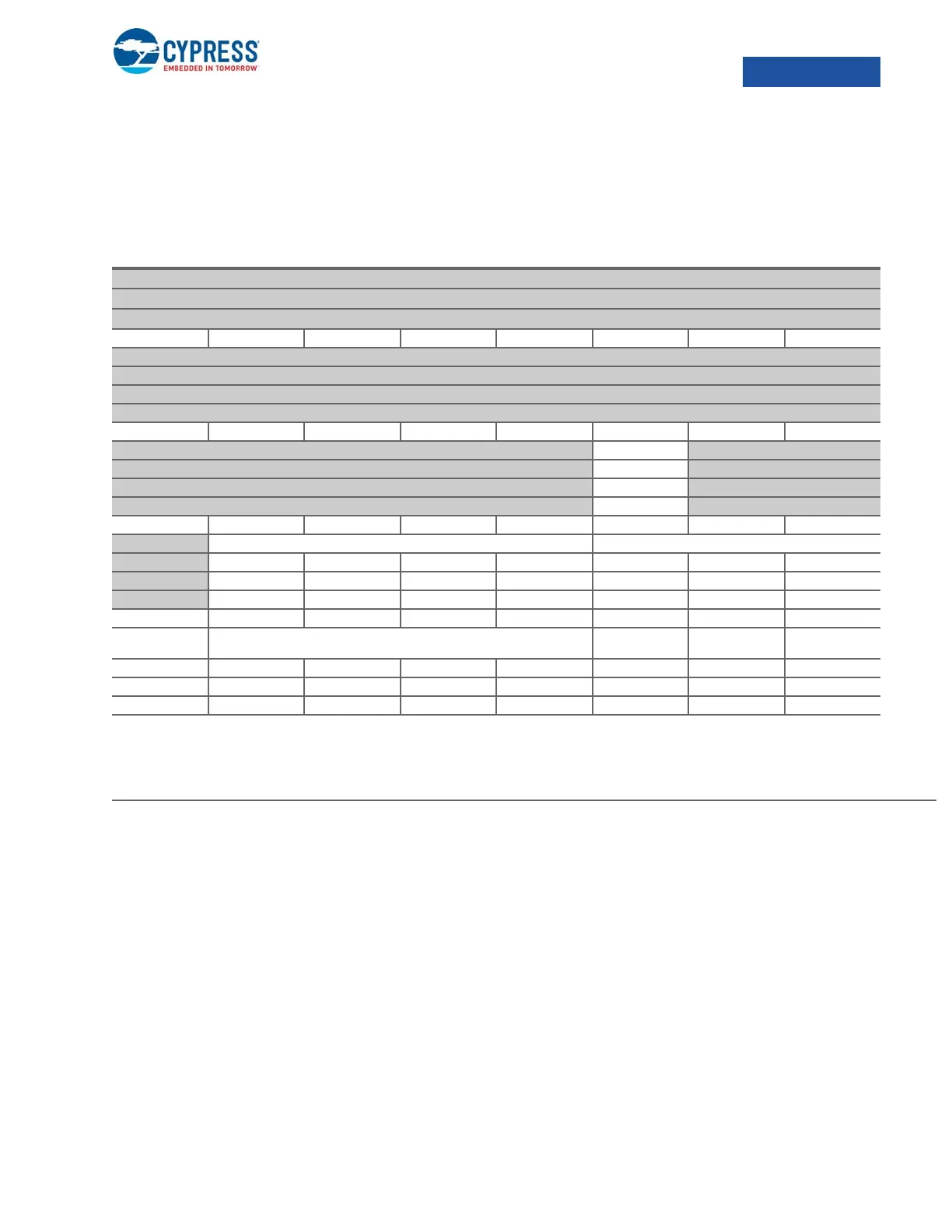

SDMMC_DLL_CTRL

0xFC

10.26.27 SDMMC_DLL_CTRL

SDMMC DLL Control Register

This register is used to configure the SIB DLL. Note that the use of SIB DLL is not recommended; also, the DLL should be

kept disabled. There are two copies of this register corresponding to the two storage ports. The address of each register is

calculated as 0xe0020058 + (port * 0x0400).

18 DLL_RESET_N 1: Bring DLL out of reset

0: Keep DLL in reset.

14:11 PIN_CLOCK_PHASE_SEL Select clock phase (0–15) to be driven out on the SD_CLK pin.

10:7 SAMPLE_CMD_PHASE_SEL Select clock phase (0–15) used to sample the SD_CMD pin to look for response.

6:3 SAMPLE_DATA_PHASE_SEL Select clock phase (0–15) used to sample the SD_DAT[] pins to get read data.

2 DLL_STAT Reflects DLL lock status.

1: DLL is locked.

0: DLL is not locked.

1HIGH_FREQ Select high frequency mode of DLL operation.

0: Use when clock frequency is less than 70 MHz.

1: Use when clock frequency is greater than 70 MHz.

0 ENABLE 1: Enable the SIB DLL

0: Disable the SIB DLL

SDMMC_DLL_CTRL

SDMMC DLL Control

0xE0020058

b31 b30 b29 b28 b27 b26 b25 b24

b23 b22 b21 b20 b19 b18 b17 b16

DLL_RESET_N

R

R/W

0

b15 b14 b13 b12 b11 b10 b9 b8

PIN_CLOCK_PHASE_SEL[3:0] SAMPLE_CMD_PHASE_SEL[3:1]

RRRRRRR

R/W R/W R/W R/W R/W R/W R/W

0000000

b7 b6 b5 b4 b3 b2 b1 b0

SAMPLE_CMD_P

HASE_SEL[0]

SAMPLE_DATA_PHASE_SEL[3:0] DLL_STAT HIGH_FREQ ENABLE

RRRRRR/WRR

R/W R/W R/W R/W R/W R R/W R/W

00000000

Bit Name Description

Loading...

Loading...