EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 52

Global Controller (GCTL)

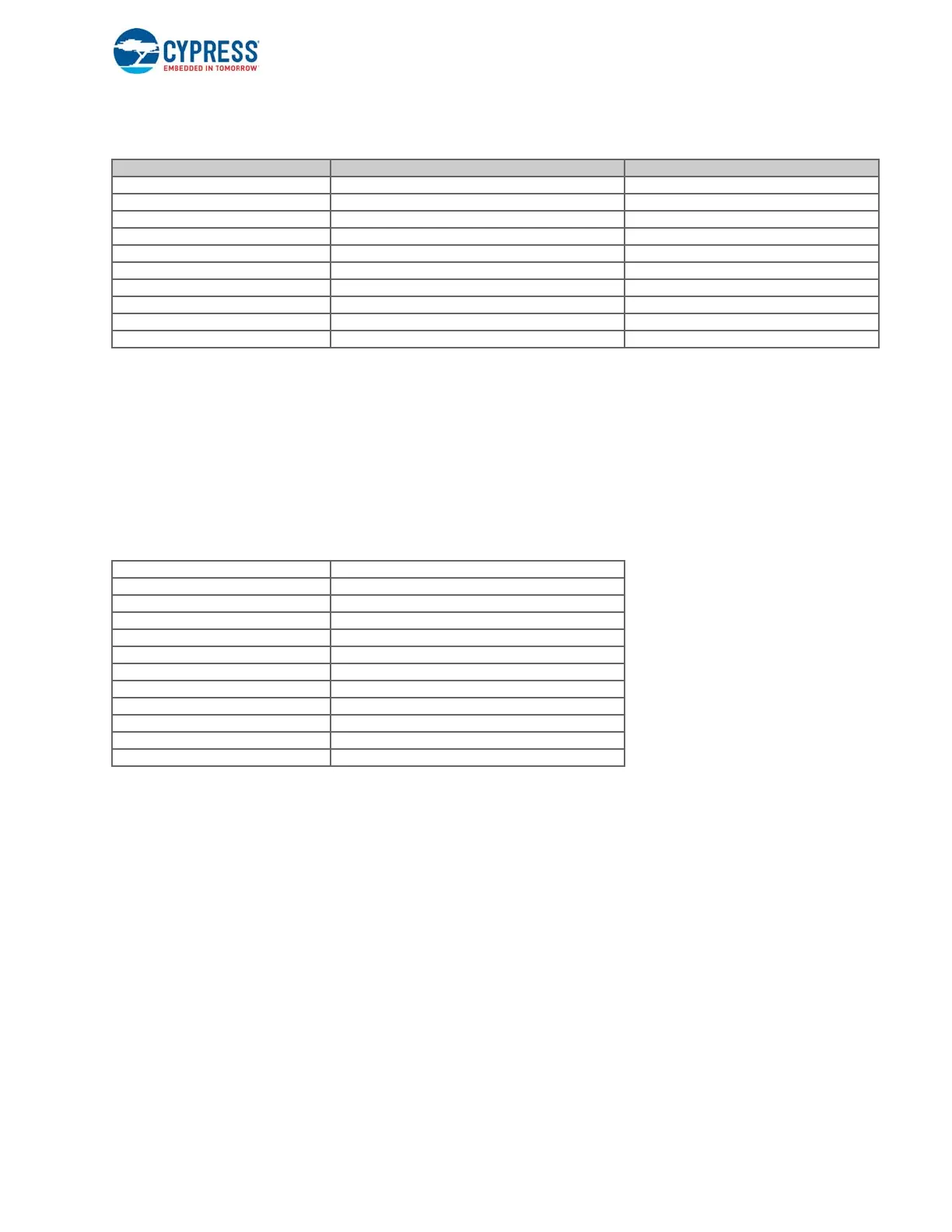

Table 4-1. I/O Pin Alternate Function(s)

* 24- or 32-bit GPIF II bus width is not supported by all FX3 chips. If the FX3 chip does not support more than a 16-bit bus

width, then alternate functions are not applicable. Refer to the EZ-USB FX3 datasheet for more details.

** If the GPIF II bus width is configured to 8, 16, or 24 bits, then UART lines are available on the GPIO[46] to GPIO[49] pins,

and SPI lines are available on the GPIO[53] to GPIO[56] pins. If the GPIF II bus width is configured to 32 bits, then UART

lines are available on the GPIO[53] to GPIO[56] pins, and SPI is not supported.

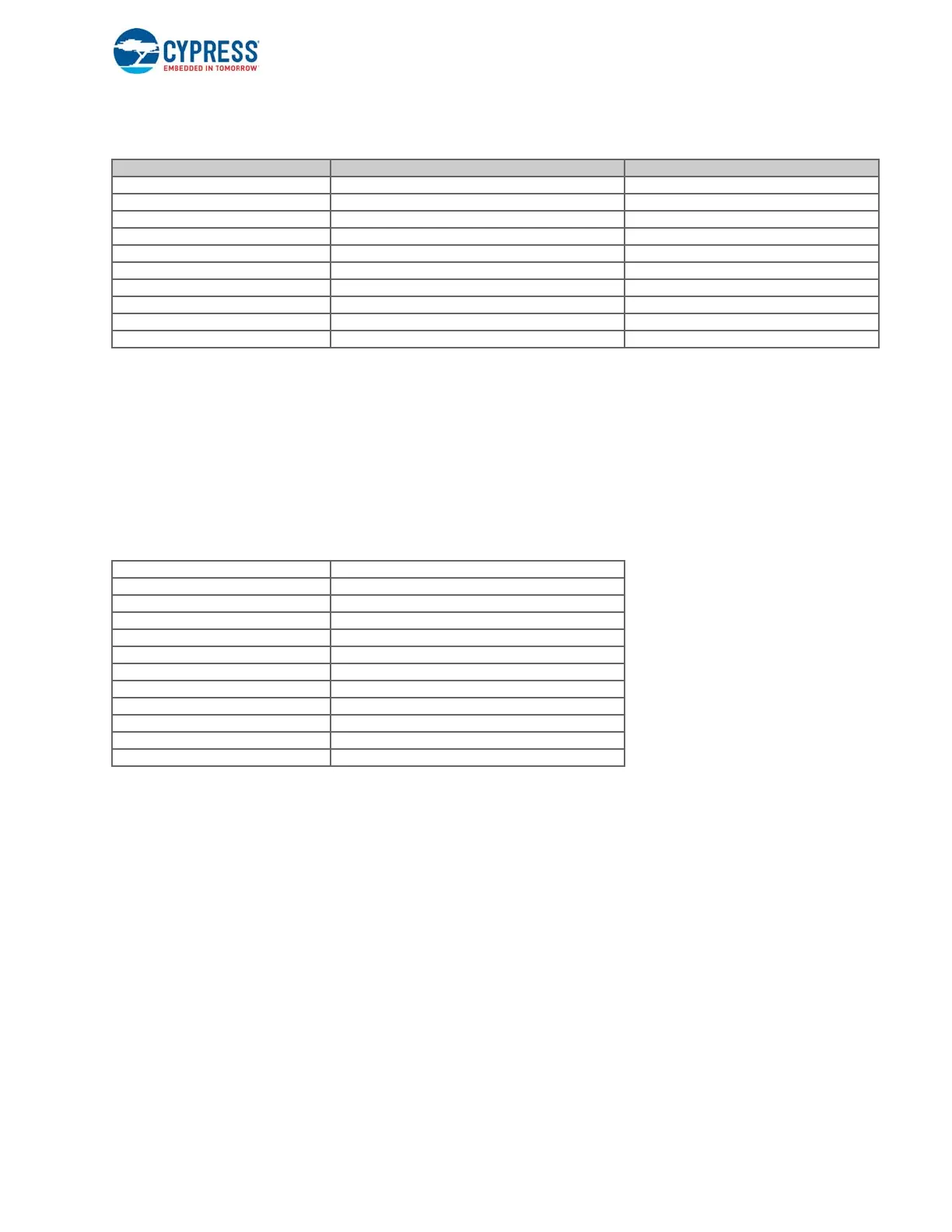

Table 4-2 lists the FX3 registers associated with GPIO pin control. These registers are described in detail in following tables.

Table 4-2. Registers Associated with GPIO Pins

See I/O Matrix Configuration Register on page 240

The FX3 SDK API CyU3PDeviceConfigureIOMatrix configures the GCTL_IOMATRIX register. A code snippet to configure the

I/O matrix follows. Refer to the SDK firmware example for the complete details on the IOMATRIX configuration.

/* Configure the IO matrix for the device.

* 32 bit bus width is disabled.

* S0 port is disabled.

* S1 port is disabled.

* UART is enabled on S1 port.

* IOs 43, 45, 52 and 57 are chosen as GPIO. */

*/

io_cfg.isDQ32Bit = CyFalse;

io_cfg.s0Mode = CY_U3P_SPORT_INACTIVE;

io_cfg.s1Mode = CY_U3P_SPORT_INACTIVE;

io_cfg.gpioSimpleEn[0] = 0;

io_cfg.gpioSimpleEn[1] = 0x02102800;

io_cfg.gpioComplexEn[0] = 0;

io_cfg.gpioComplexEn[1] = 0;

Pin Names Alternate Function Comments

GPIO[0] to GPIO[15] DQ[0] to DQ[15] GPIF II data pins

GPIO[16] PCLK or CLK GPIF II clock pin

GPIO[17] to GPIO[29] CTL[x] GPIF II control pins

GPIO[30] to GPIO[32] PMOD[x] Boot mode

GPIO[33] to GPIO[44]* DQ[16] to DQ[27] GPIF II data pins

GPIO[45] - No alternate function

GPIO[46] to GPIO[49]** DQ[28] to DQ[31] or UART GPIF II data pins or UART pins

GPIO[50] to GPIO[52] and GPIO[57] I2S

GPIO[53] to GPIO[56]** SPI or UART

GPIO[58] to GPIO[59] I2C

GCTL_IOMATRIX GCTL_DS

GCTL_WPU_CFG0 GCTL_WPU_CFG1

GCTL_WPD_CFG0 GCTL_WPD_CFG1

GCTL_GPIO_SIMPLE0 GCTL_GPIO_SIMPLE1

GCTL_GPIO_COMPLEX0 GCTL_GPIO_COMPLEX1

LPP_GPIO_ID LPP_GPIO_POWER

LPP_GPIO_PIN_STATUS(n) LPP_GPIO_PIN_TIMER(n)

LPP_GPIO_PIN_THRESHOLD(n) LPP_GPIO_SIMPLE(n)

LPP_GPIO_DRIVE_LO_EN LPP_GPIO_DRIVE_HI_EN

LPP_GPIO_INPUT_EN LPP_GPIO_PIN_INTR

LPP_GPIO_INVALUE0 LPP_GPIO_INVALUE1

LPP_GPIO_INTR0_REG LPP_GPIO_INTR1_REG

Loading...

Loading...