SEC-CDR (SEC-CDR Link Maintenance)

Issue 4 May 2002

10-1483555-233-123

SEC-CDR (SEC-CDR Link

Maintenance)

The SEC-CDR (SEC-CDR Link) maintenance strategy is covered in the

PRI-CDR/SEC-CDR (PRI-CDR Link) Maintenance documentation.

SHDW-CIR (Common Shadow

Circuit)

The Common Shadow Circuit is that portion of the Duplication Interface circuit

pack that is responsible for memory shadowing in a High or Critical Reliability

system. All memory writes on the active SPE are detected by the Common

Shadow Circuit on the active Duplication Interface circuit pack through the

Memory Bus (M-BUS—bus used by control complex circuit packs to write/read

memory and to communicate with one another). The write information is then

passed to the Common Shadow Circuit on the Standby Duplication Interface

circuit pack via the ICC which then executes the write to memory. In this way, the

Standby SPE is kept up-to-date with the Active SPE and, as a result, is always

ready to take over for the Active SPE.

Refer to DUPINT (Duplication Interface Circuit Pack) Maintenance documentation

for a detailed description of SPE-to-SPE connectivity and STBY-SPE (Standby

SPE) Maintenance documentation for a description of how the Standby SPE is

maintained.

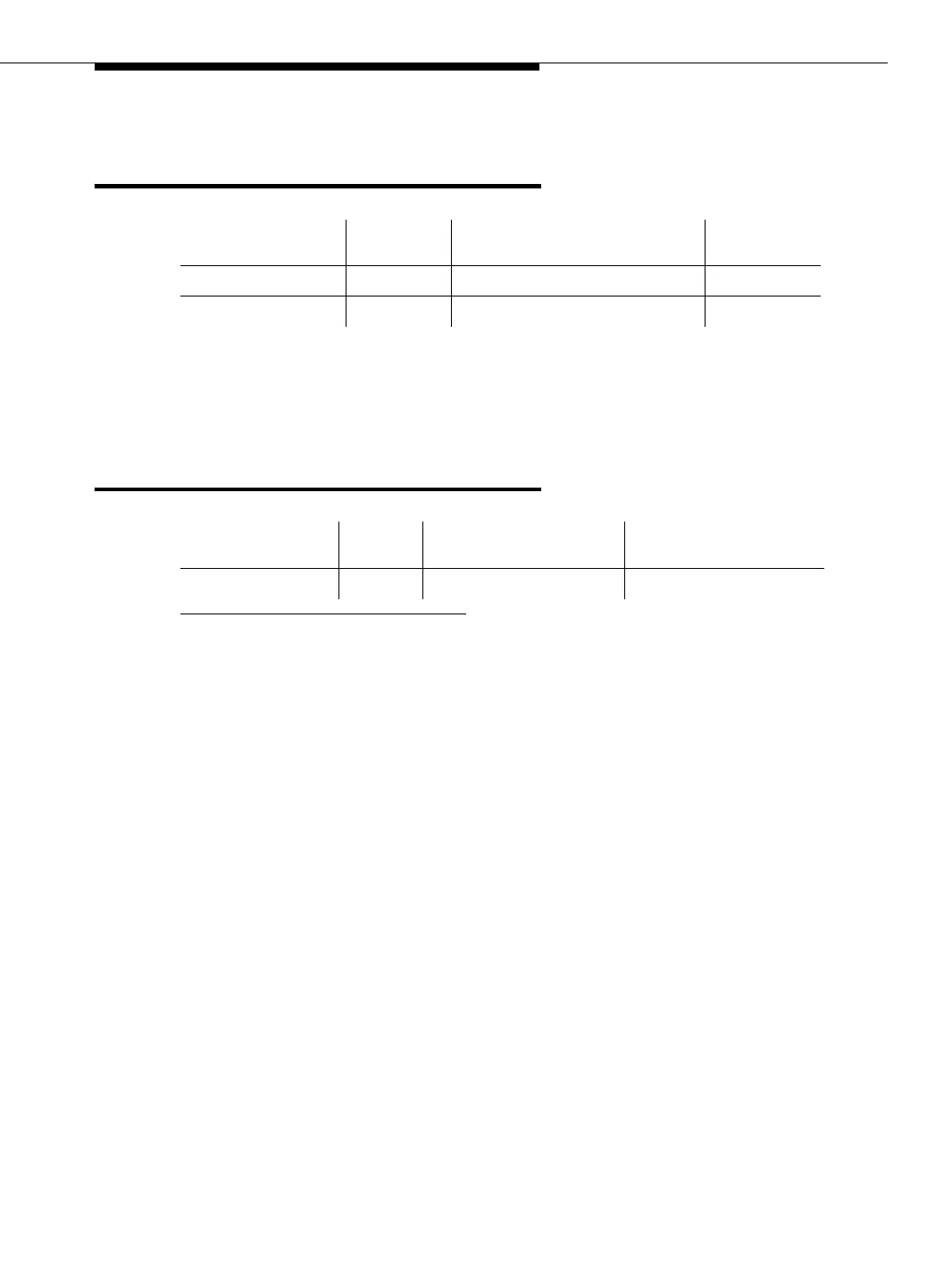

MO Name (in

Alarm Log)

Alarm

Level Initial Command to Run

Full Name

of MO

PRI-CDR/SEC-CDR MINOR test cdr-link primary/secondary l CDR Link

PRI-CDR/SEC-CDR WARNING test cdr-link primary/secondary CDR Link

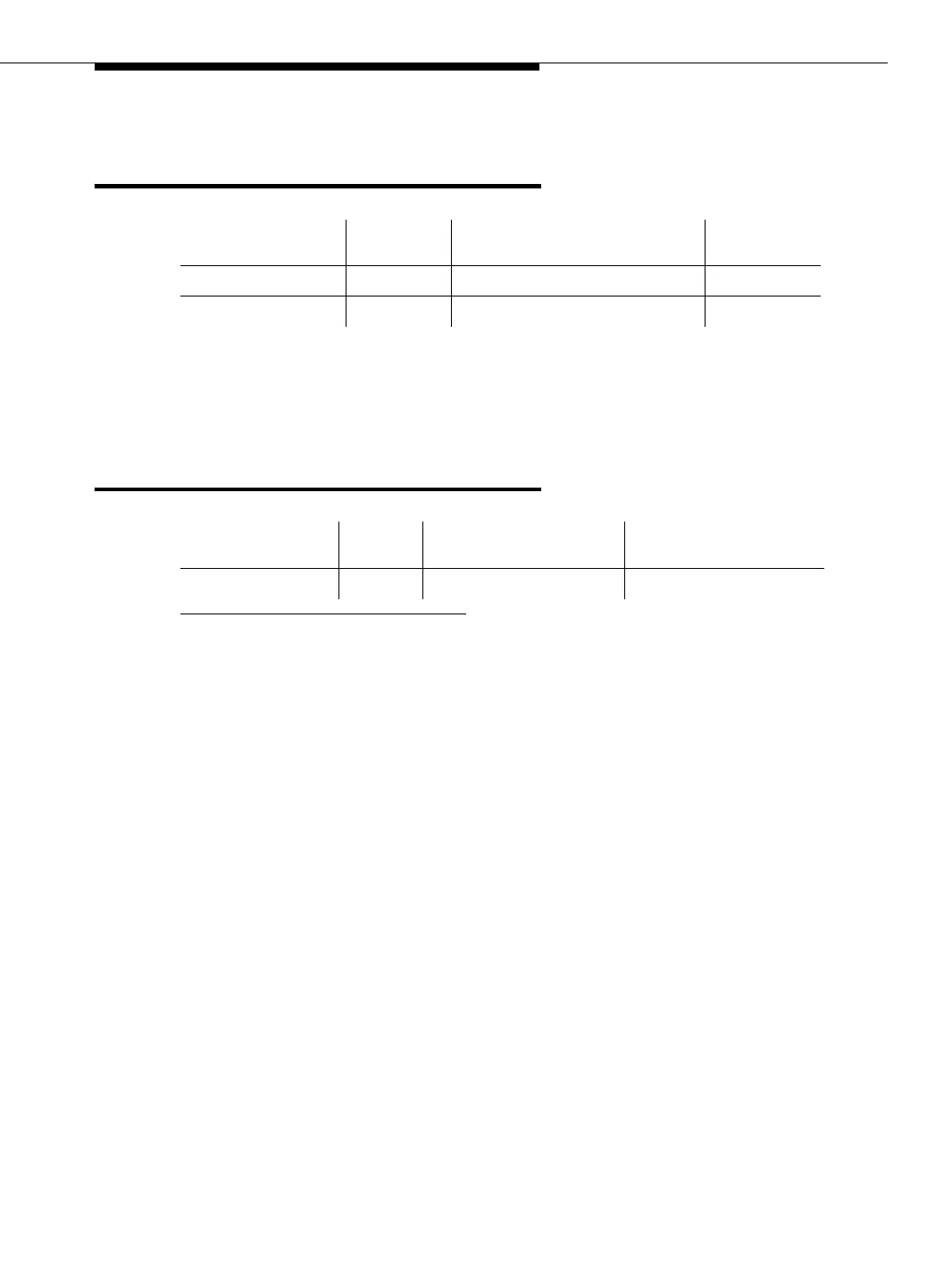

MO Name (in

Alarm Log)

Alarm

Level Initial Command to Run Full Name of MO

SHDW-CIR

1

1 Determine the carrier to test via the Port field from the Alarm or Error Log.

MAJOR test duplication 1C sh Common Shadow Circuit

Loading...

Loading...