USB on-the-go high-speed (OTG_HS) RM0090

1293/1422 Doc ID 018909 Rev 4

These data indicate that a SETUP packet for the specified endpoint is now

available for reading from the receive FIFO.

c) Setup stage done pattern:

PKTSTS = Setup Stage Done, BCNT = 0x0, EPNUM = Control EP Num,

DPID = Don’t Care (0b00).

These data indicate that the Setup stage for the specified endpoint has completed

and the Data stage has started. After this entry is popped from the receive FIFO,

the core asserts a Setup interrupt on the specified control OUT endpoint.

d) Data OUT packet pattern:

PKTSTS = DataOUT, BCNT = size of the received data OUT packet (0 ≤ BCNT

≤ 1 024), EPNUM = EPNUM on which the packet was received, DPID = Actual

Data PID.

e) Data transfer completed pattern:

PKTSTS = Data OUT Transfer Done, BCNT = 0x0, EPNUM = OUT EP Num

on which the data transfer is complete, DPID = Don’t Care (0b00).

These data indicate that an OUT data transfer for the specified OUT endpoint has

completed. After this entry is popped from the receive FIFO, the core asserts a

Transfer Completed interrupt on the specified OUT endpoint.

5. After the data payload is popped from the receive FIFO, the RXFLVL interrupt

(OTG_HS_GINTSTS) must be unmasked.

6. Steps 1–5 are repeated every time the application detects assertion of the interrupt line

due to RXFLVL in OTG_HS_GINTSTS. Reading an empty receive FIFO can result in

undefined core behavior.

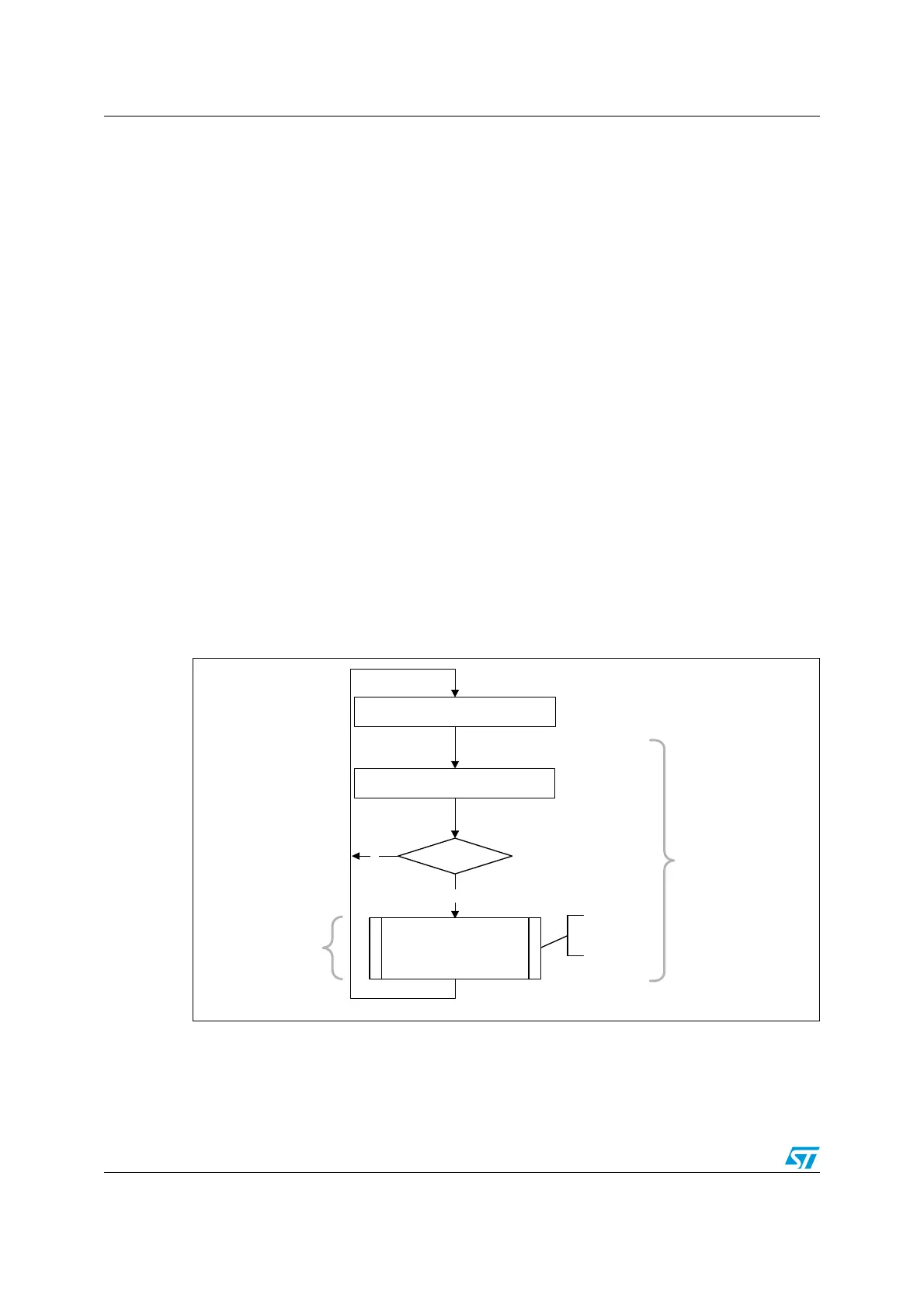

Figure 395 provides a flowchart of the above procedure.

Figure 395. Receive FIFO packet read in slave mode

● SETUP transactions

This section describes how the core handles SETUP packets and the application’s

sequence for handling SETUP transactions.

● Application requirements

dword_cnt =

BCNT[11:2] +C

(

BCNT[1]

| BCNT[1])

rcv_out_pkt()

rd_data = rd_reg (OTG_FS_GRXSTSP);

mem[0:dword_cnt-1] =

rd_rxfifo(rd_data.EPNUM,

dword_cnt)

N

rd_data.BCNT = 0

wait until RXFLVL in OTG_FS_GINTSTSG

packet

store in

memory

Y

ai15677

Loading...

Loading...