Ethernet (ETH): media access control (MAC) with DMA controller RM0090

1017/1422 Doc ID 018909 Rev 4

Ethernet DMA current host receive buffer address register

(ETH_DMACHRBAR)

Address offset: 0x1054

Reset value: 0x0000 0000

The current host receive buffer address register points to the current receive buffer address

being read by the DMA.

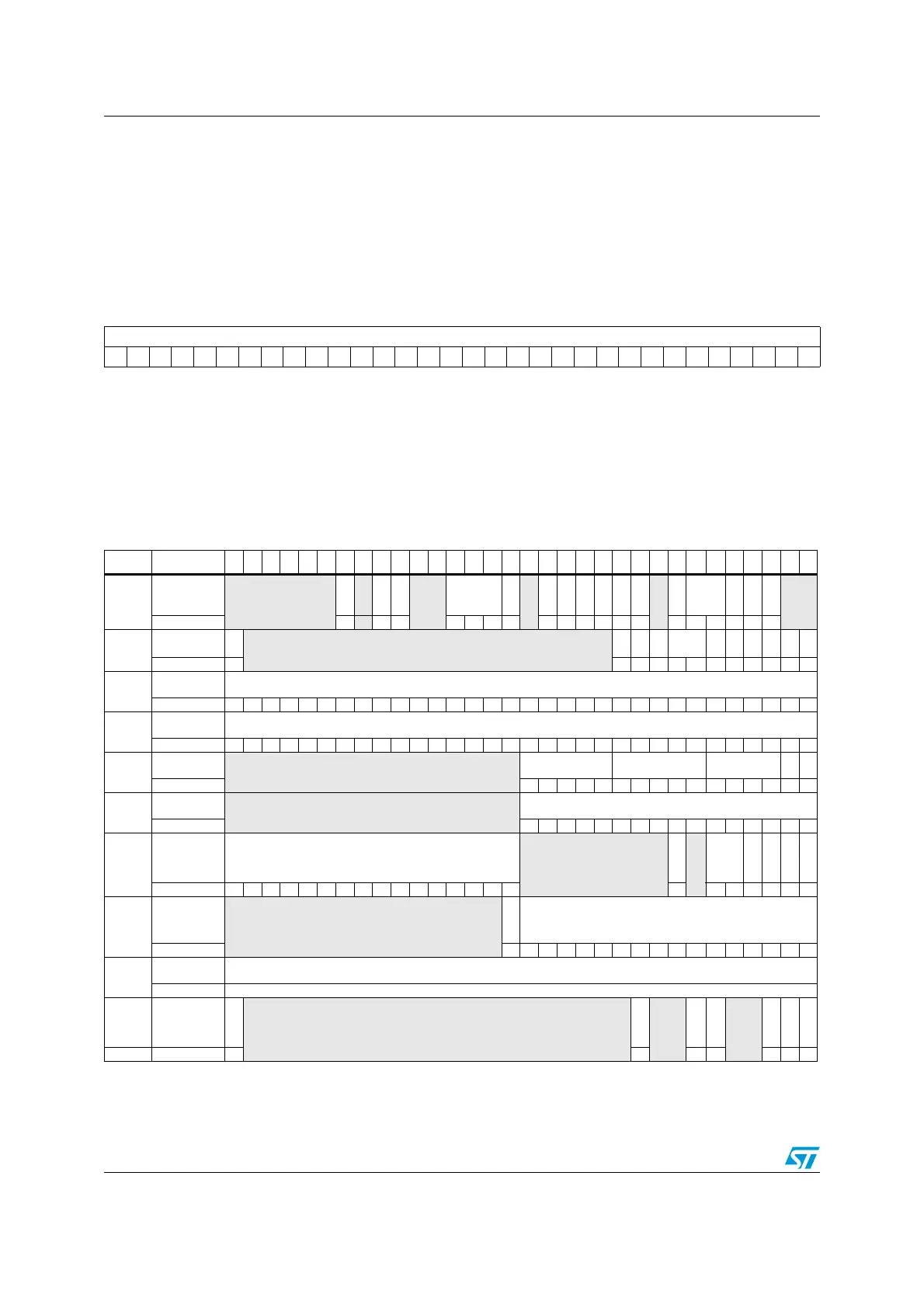

29.8.5 Ethernet register maps

Table 170 gives the ETH register map and reset values.

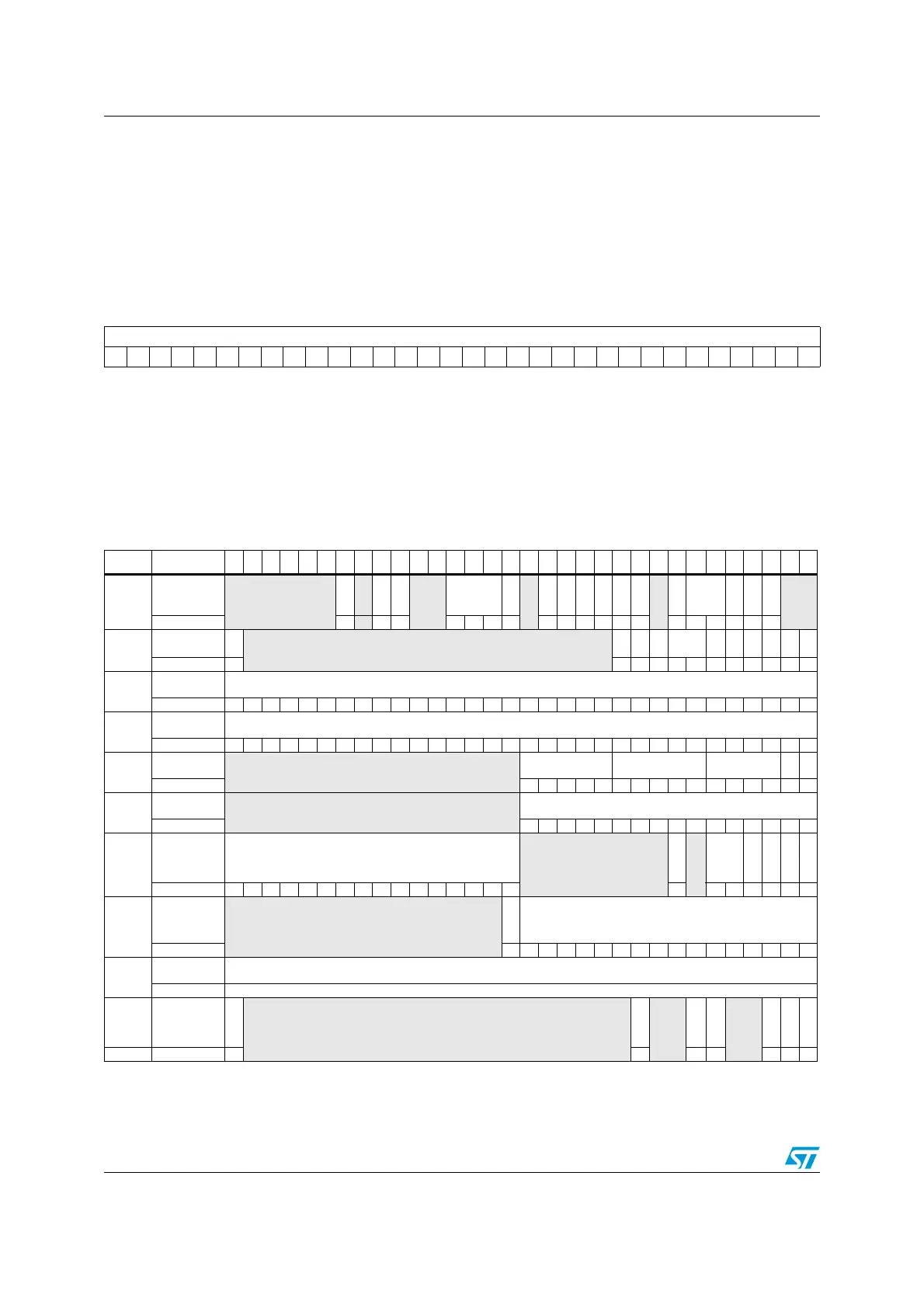

313029282726252423222120191817161514131211109876543210

HRBAP

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 HRBAP: Host receive buffer address pointer

Cleared on reset. Pointer updated by DMA during operation.

Table 170. Ethernet register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

ETH_MACCR

Reserved

CSTF

eserved

WD

JD

Reserved

IFG

CSD

Reserved

FES

ROD

LM

DM

IPCO

RD

Reserved

APCS

BL

DC

TE

RE

Reserved

Reset value 0 00 0000 000000 000000

0x04

ETH_MACFF

R

RA

Reserved

HPF

SAF

PCF

BFD

PAM

DAIF

HM

HU

PM

Reset value 0 00000000000

0x08

ETH_MACHT

HR

HTH[31:0]

Reset value 00000000000000000000000000000000

0x0C

ETH_MACHT

LR

HTL[31:0]

Reset value 00000000000000000000000000000000

0x10

ETH_MACMII

AR

Reserved

PA M R

CR

M

W

M

B

Reset value 0000000000000000

0x14

ETH_MACMII

DR

Reserved

MD

Reset value 0000000000000000

0x18

ETH_MACFC

R

PT

Reserved

ZQPD

Reserved

PLT

UPFD

RFCE

TFCE

FCB/BPA

Reset value 0000000000000000 0 000000

0x1C

ETH_MACVL

ANTR

Reserved

VLANTC

VLANTI

Reset value 00000000000000000

0x28

ETH_MACRW

UFFR

Frame filter reg0\Frame filter reg1\Frame filter reg2\Frame filter reg3\Frame filter reg4\...\Frame filter reg7

Reset value 0

0x2C

ETH_MACPM

TCSR

WFFRPR

Reserved

GU

Reserved

WFR

MPR

Reserved

WFE

MPE

PD

Reset value 0 0 00 000

Loading...

Loading...