RM0090 Hash processor (HASH)

Doc ID 018909 Rev 4 612/1422

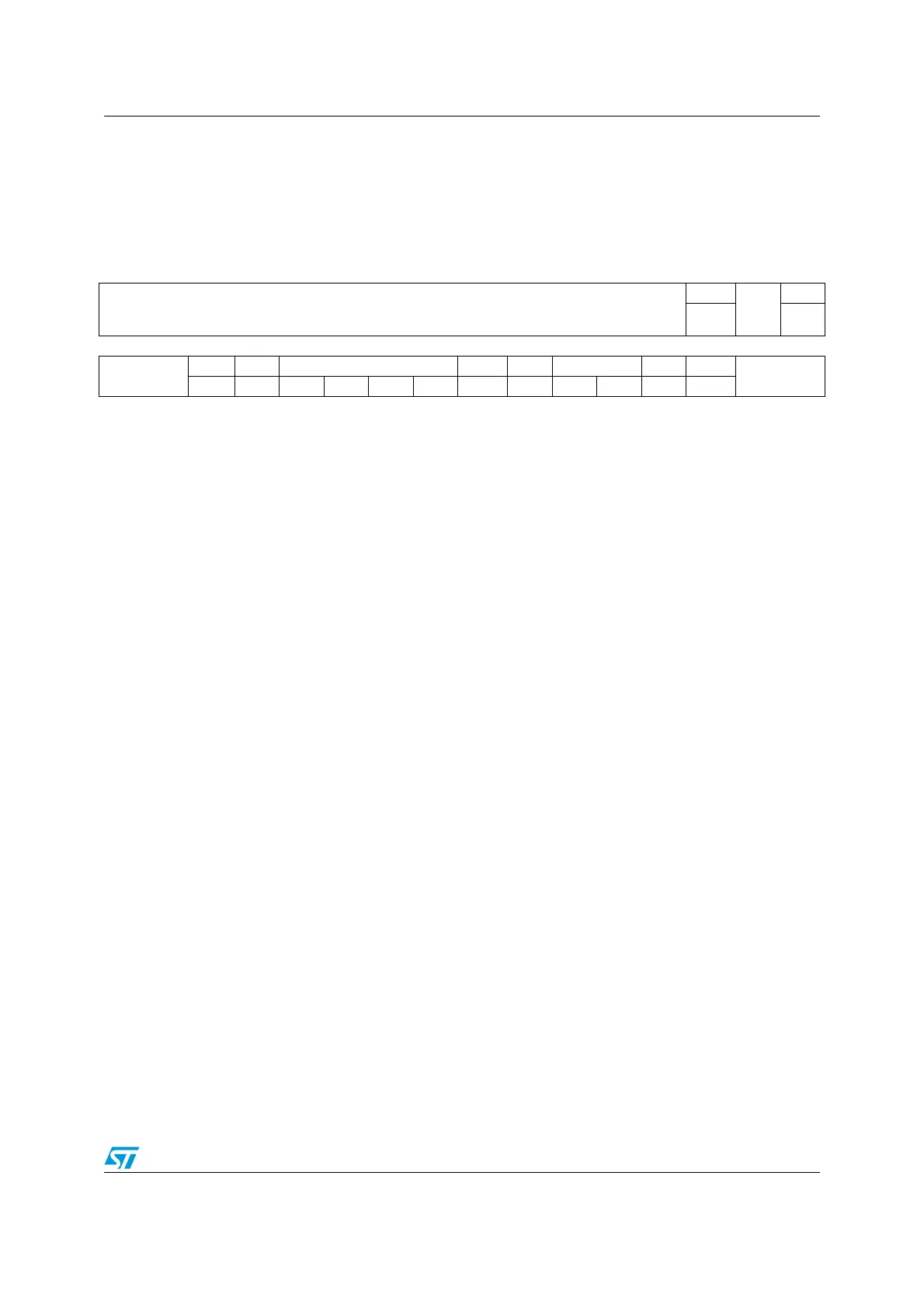

22.4.2 HASH control register (HASH_CR) for

STM32F42xxx and STM32F43xxx

Address offset: 0x00

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

ALGO[1]

Reserved

LKEY

rw rw

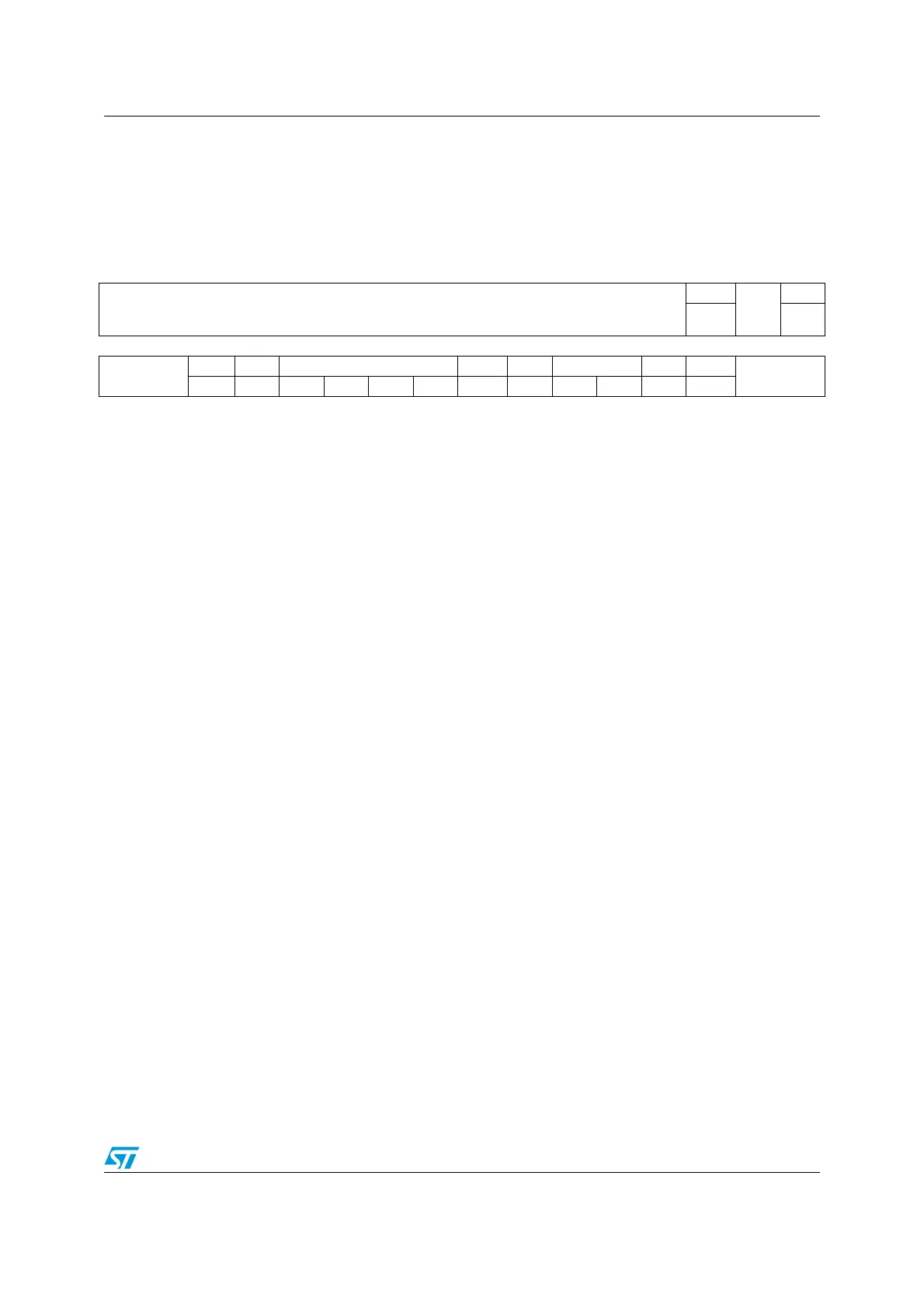

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

MDMAT DINNE NBW ALGO[0] MODE DATATYPE DMAE INIT

Reserved

rwrrrrrrwrwrwrwrww

Bits 31:19 Reserved, forced by hardware to 0.

Bit 17 Reserved, forced by hardware to 0.

Bit 16 LKEY: Long key selection

This bit selects between short key (≤ 64 bytes) or long key (> 64 bytes) in HMAC

mode

0: Short key (≤ 64 bytes)

1: Long key (> 64 bytes)

Note: This selection is only taken into account when the INIT bit is set and MODE

= 1. Changing this bit during a computation has no effect.

Bits 15:14 Reserved, forced by hardware to 0.

Bit 13 MDMAT: Multiple DMA Transfers

This bit is set when hashing large files when multiple DMA transfers are needed.

0: DCAL is automatically set at the end of a DMA transfer.

1: DCAL is not automatically set at the end of a DMA transfer.

Bit 12 DINNE: DIN not empty

This bit is set when the HASH_DIN register holds valid data (that is after being

written at least once). It is cleared when either the INIT bit (initialization) or the

DCAL bit (completion of the previous message processing) is written to 1.

0: No data are present in the data input buffer

1: The input buffer contains at least one word of data

Loading...

Loading...