RM0090 Ethernet (ETH): media access control (MAC) with DMA controller

Doc ID 018909 Rev 4 906/1422

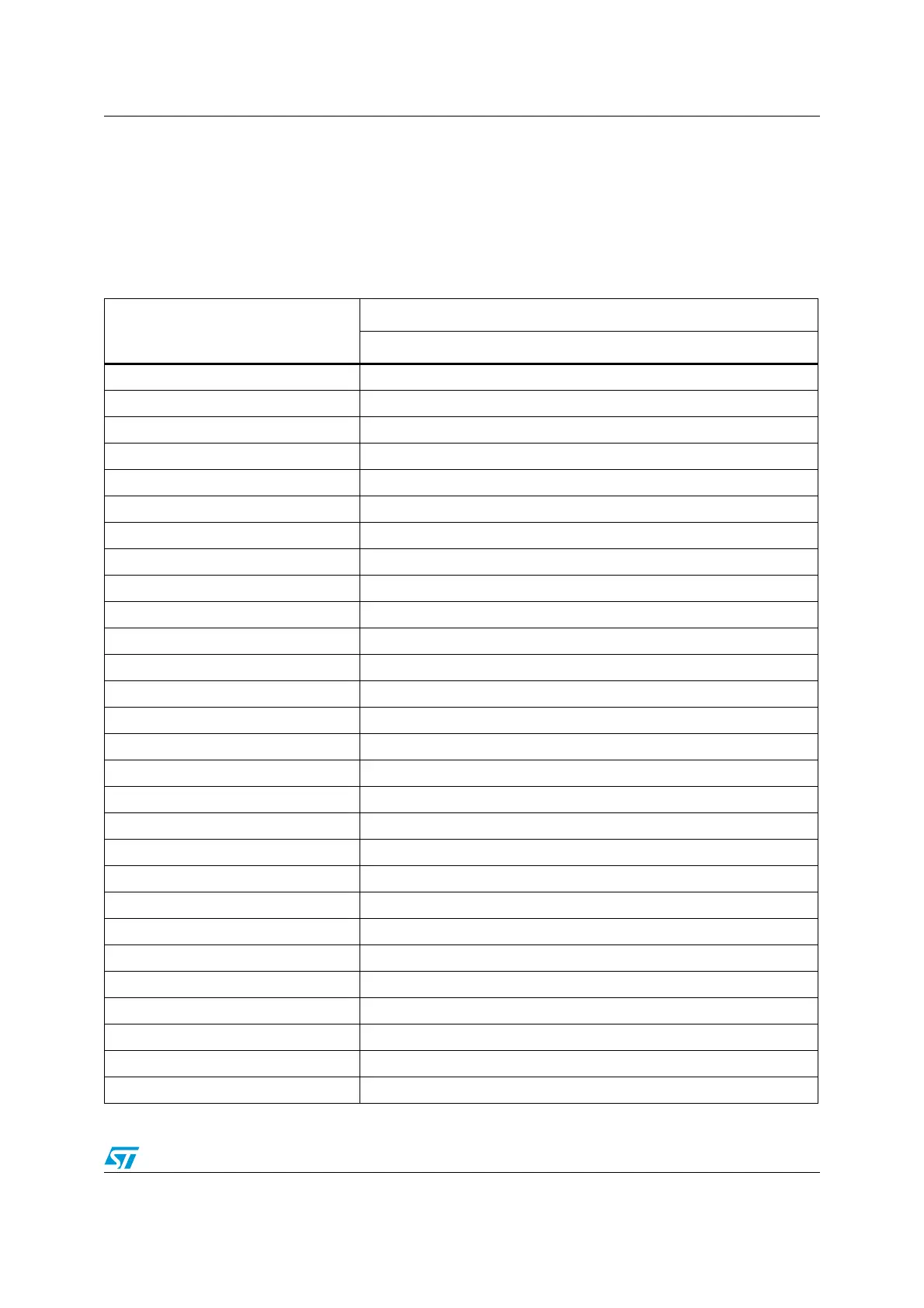

29.3 Ethernet pins

Table 160 shows the MAC signals and the corresponding MII/RMII signal mapping. All MAC

signals are mapped onto AF11, some signals are mapped onto different I/O pins, and

should be configured in Alternate function mode (for more details, refer to Section 7.3.2: I/O

pin multiplexer and mapping).

Table 160. Alternate function mapping

Port

AF11

ETH

PA0-WKUP ETH_MII_CRS

PA1 ETH_MII _RX_CLK / ETH_RMII _REF_CLK

PA2 ETH _ MDI O

PA3 ETH _MII_COL

PA7 ETH_MII _RX_DV / ETH_RMII _CRS_DV

PB0 ETH _MII_RXD2

PB1 ETH _MII_RXD3

PB5 ETH _PPS_OUT

PB8 ETH _MII_TXD3

PB10 ETH_ MII_RX_ER

PB11 ETH _MII_TX_EN / ETH _RMII_TX_EN

PB12 ETH _MII_TXD0 / ETH _RMII_TXD0

PB13 ETH _MII_TXD1 / ETH _RMII_TXD1

PC1 ETH _MDC

PC2 ETH _MII_TXD2

PC3 ETH _MII_TX_CLK

PC4 ETH_MII_RXD0 / ETH_RMII_RXD0

PC5 ETH _MII_RXD1/ ETH _RMII_RXD1

PE2 ETH_MII_TXD3

PG8 ETH_PPS_OUT

PG11 ETH _MII_TX_EN / ETH _RMII_TX_EN

PG13 ETH _MII_TXD0 / ETH _RMII_TXD0

PG14 ETH _MII_TXD1 / ETH _RMII_TXD1

PH2 ETH _MII_CRS

PH3 ETH _MII_COL

PH6 ETH _MII_RXD2

PH7 ETH _MII_RXD3

PI10 ETH _MII_RX_ER

Loading...

Loading...