Flexible static memory controller (FSMC) RM0090

1327/1422 Doc ID 018909 Rev 4

32.5.4 NOR Flash/PSRAM controller asynchronous transactions

Asynchronous static memories (NOR Flash memory, PSRAM, SRAM)

● Signals are synchronized by the internal clock HCLK. This clock is not issued to the

memory

● The FSMC always samples the data before de-asserting the chip select signal NE. This

guarantees that the memory data-hold timing constraint is met (chip enable high to

data transition, usually 0 ns min.)

● If the extended mode is enabled (EXTMOD bit is set in the FSMC_BCRx register), up

to four extended modes (A, B, C and D) are available. It is possible to mix A, B, C and D

modes for read and write operations. For example, read operation can be performed in

mode A and write in mode B.

● If the extended mode is disabled (EXTMOD bit is reset in the FSMC_BCRx register),

the FSMC can operate in Mode1 or Mode2 as follows:

– Mode 1 is the default mode when SRAM/CRAM memory type is selected (MTYP =

0x0 or 0x01 in the FSMC_BCRx register)

– Mode 2 is the default mode when NOR memory type is selected (MTYP = 0x10 in

the FSMC_BCRx register).

Mode 1 - SRAM/PSRAM (CRAM)

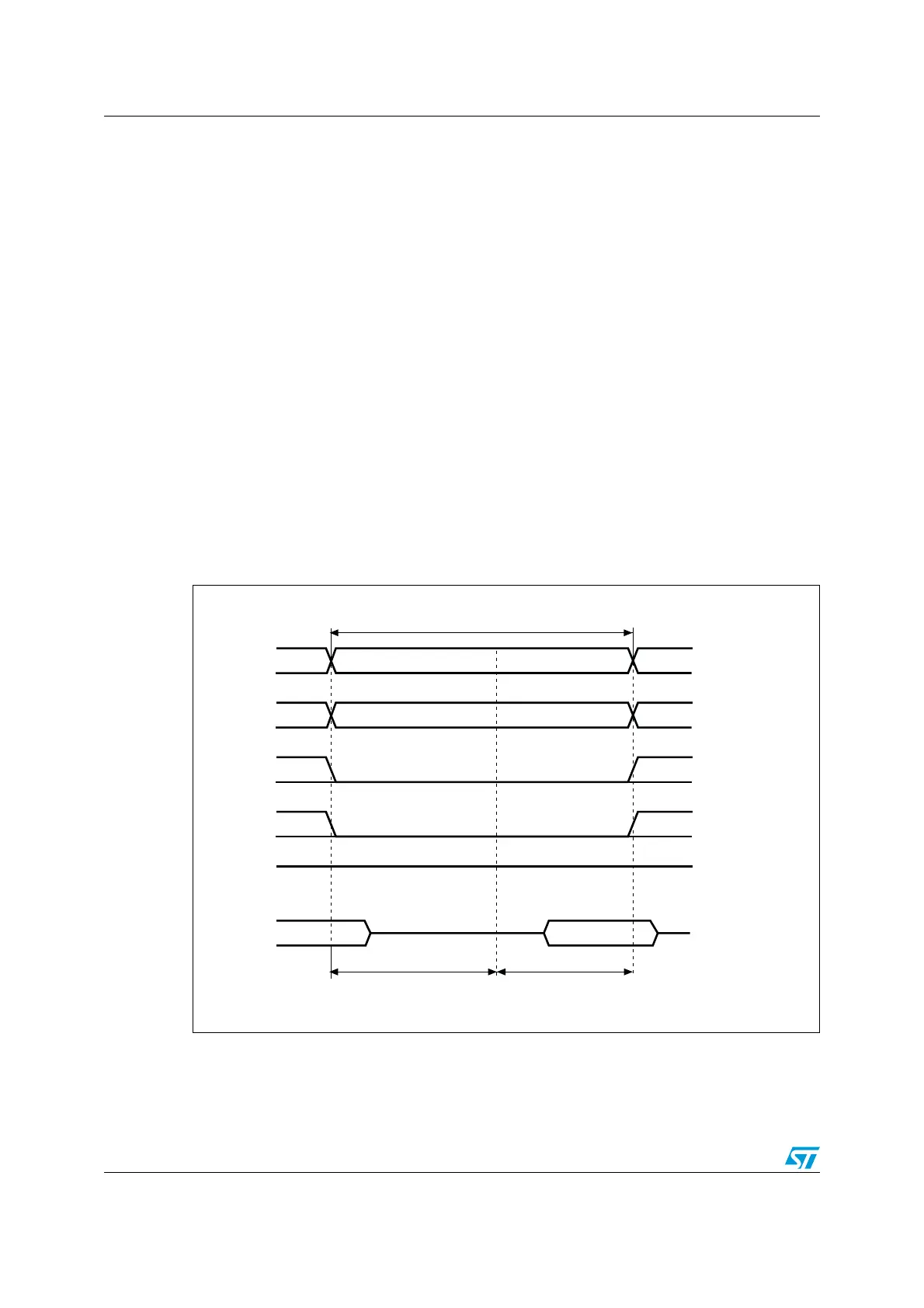

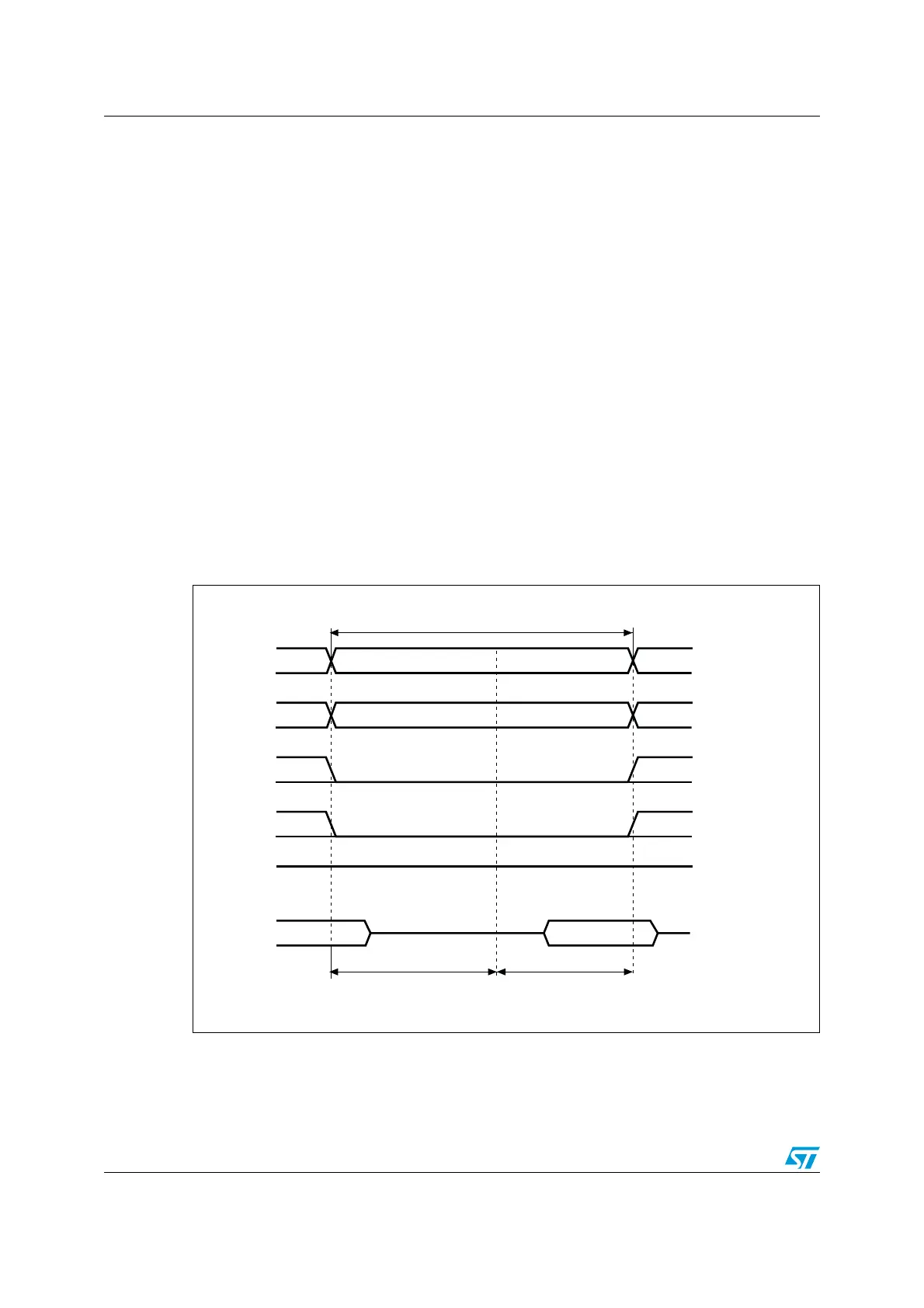

Figure 405. Mode1 read accesses

1. NBL[1:0] are driven low during read access.

A[25:0]

NOE

ADDSET DATAST

Memory transaction

NEx

D[15:0]

HCLK cycles

HCLK cycles

NWE

NBL[1:0]

data driven

by memory

ai15557

High

Loading...

Loading...