Basic timers (TIM6&TIM7) RM0090

533/1422 Doc ID 018909 Rev 4

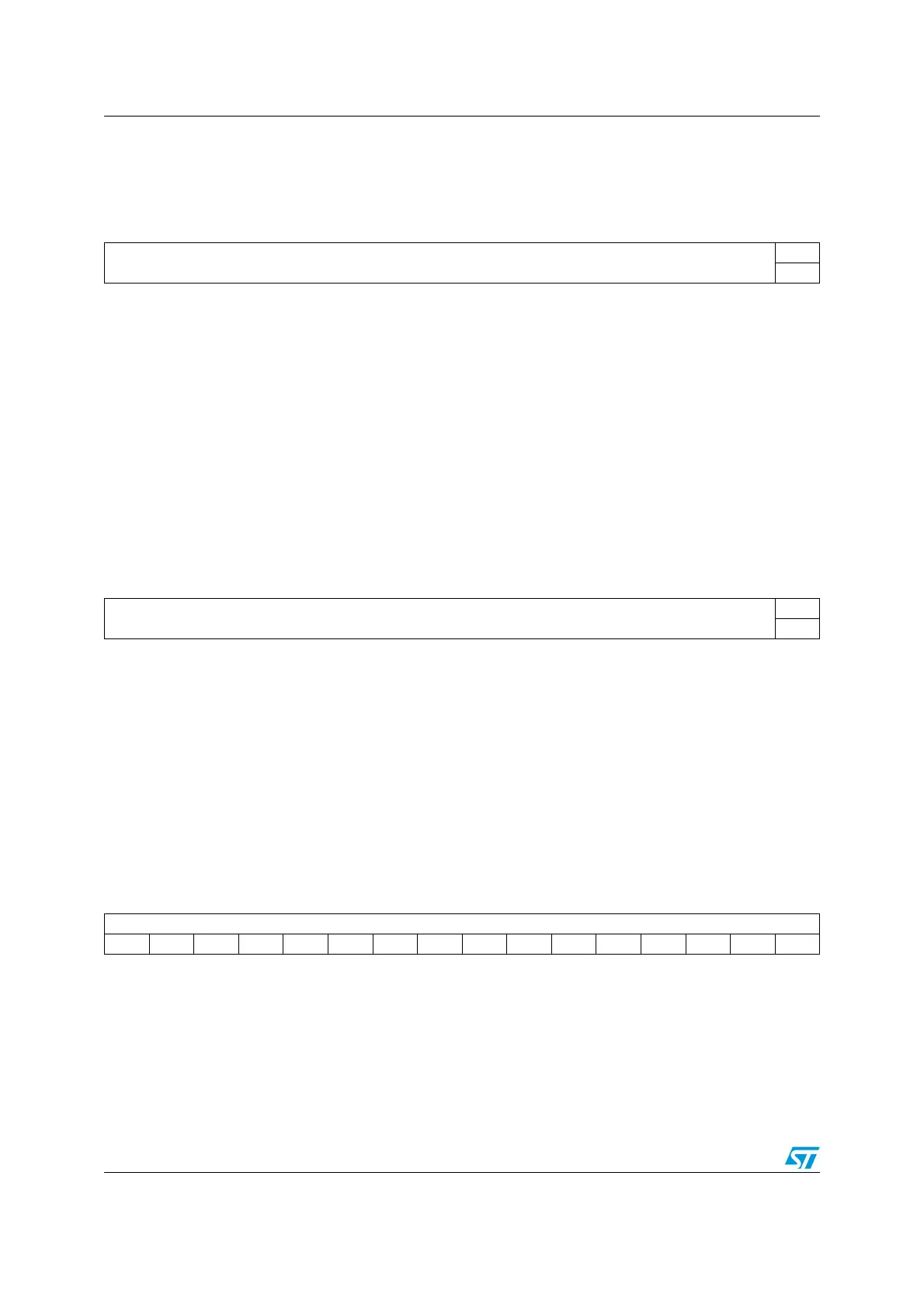

17.4.4 TIM6&TIM7 status register (TIMx_SR)

Address offset: 0x10

Reset value: 0x0000

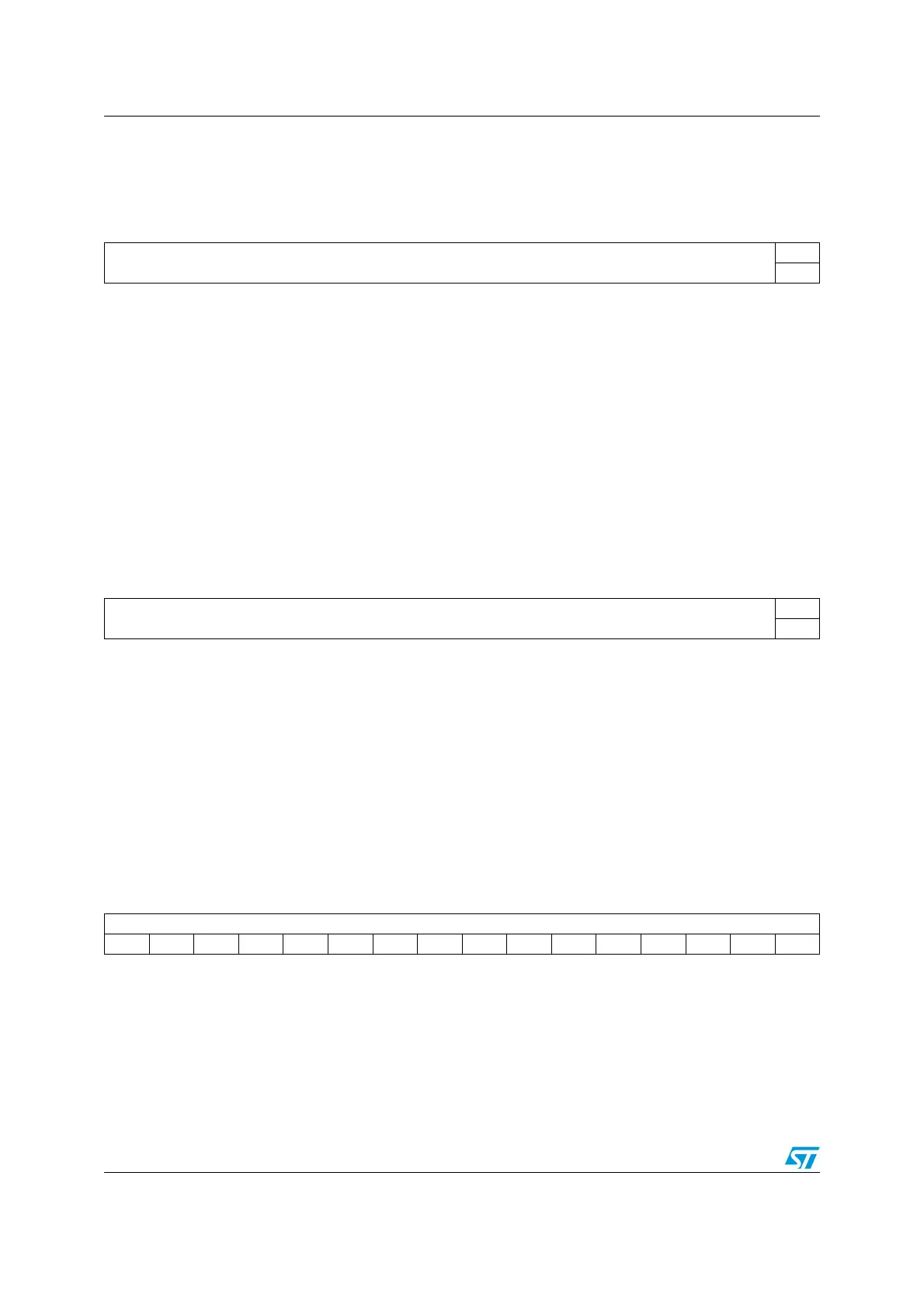

17.4.5 TIM6&TIM7 event generation register (TIMx_EGR)

Address offset: 0x14

Reset value: 0x0000

17.4.6 TIM6&TIM7 counter (TIMx_CNT)

Address offset: 0x24

Reset value: 0x0000

1514131211109876543210

Reserved

UIF

rc_w0

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 UIF: Update interrupt flag

This bit is set by hardware on an update event. It is cleared by software.

0: No update occurred.

1: Update interrupt pending. This bit is set by hardware when the registers are updated:

–At overflow or underflow and if UDIS = 0 in the TIMx_CR1 register.

–When CNT is reinitialized by software using the UG bit in the TIMx_EGR register, if

URS = 0 and UDIS = 0 in the TIMx_CR1 register.

1514131211109876543210

Reserved

UG

w

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 UG: Update generation

This bit can be set by software, it is automatically cleared by hardware.

0: No action.

1: Re-initializes the timer counter and generates an update of the registers. Note that the

prescaler counter is cleared too (but the prescaler ratio is not affected).

1514131211109876543210

CNT[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 CNT[15:0]: Counter value

Loading...

Loading...