Real-time clock (RTC) RM0090

649/1422 Doc ID 018909 Rev 4

Note: This register must be written in initialization mode only. The initialization must be performed

in two separate write accesses. Refer to Calendar initialization and configuration on

page 630

This register is write protected. The write access procedure is described in RTC register

write protection on page 630.

23.6.6 RTC wakeup timer register (RTC_WUTR)

Address offset: 0x14

Power-on reset value: 0x0000 FFFF

System reset: not affected

Note: This register can be written only when WUTWF is set to 1 in RTC_ISR.

This register is write protected. The write access procedure is described in RTC register

write protection on page 630.

Bits 31:24 Reserved

Bit 23 Reserved, must be kept at reset value.

Bits 22:16 PREDIV_A[6:0]: Asynchronous prescaler factor

This is the asynchronous division factor:

ck_apre frequency = RTCCLK frequency/(PREDIV_A+1)

Note: PREDIV_A [6:0]= 000000 is a prohibited value.

Bit 15 Reserved, must be kept at reset value.

Bits 14:0 PREDIV_S[14:0]: Synchronous prescaler factor

This is the synchronous division factor:

ck_spre frequency = ck_apre frequency/(PREDIV_S+1)

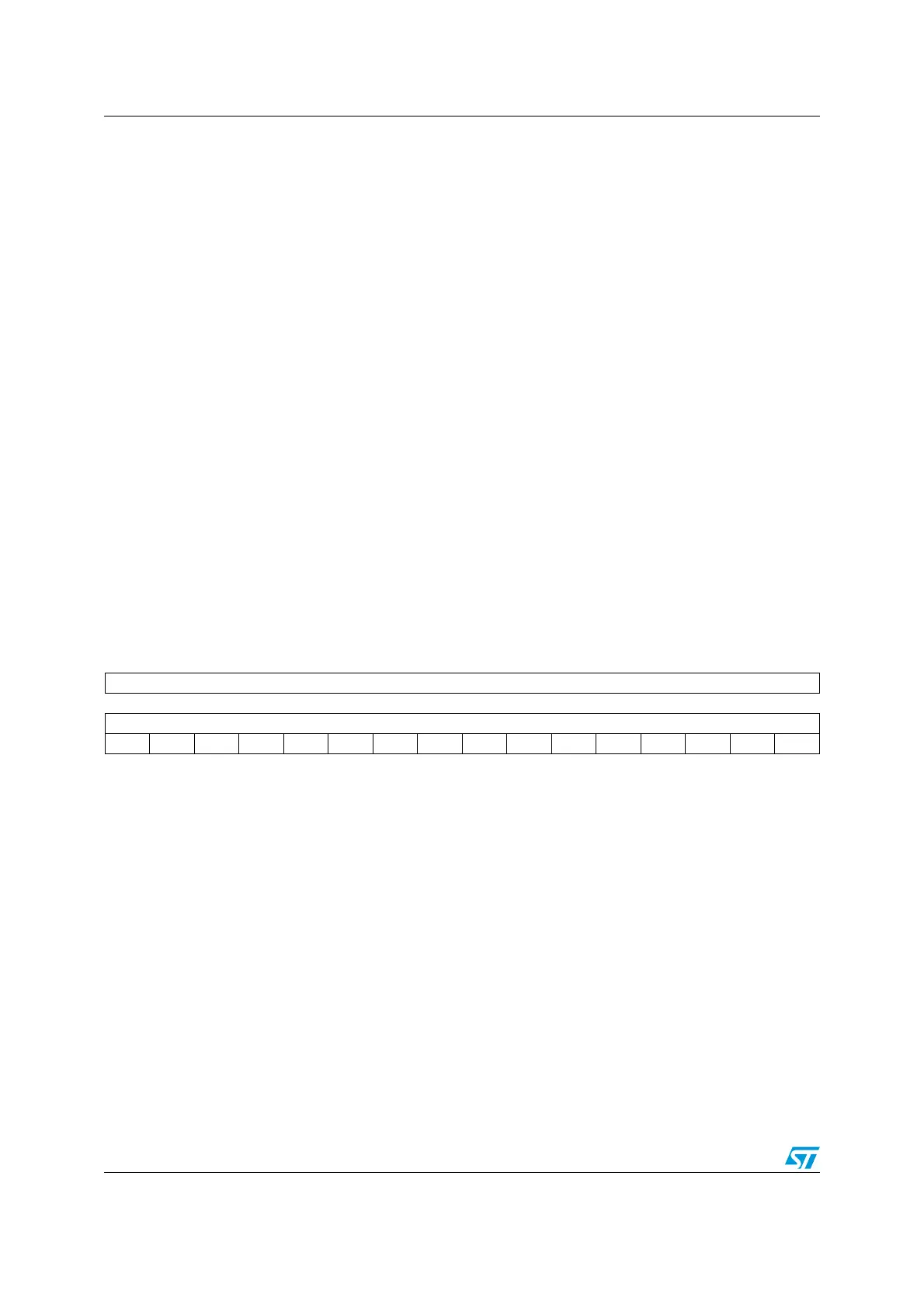

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

WUT[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved

Bits 15:0 WUT[15:0]: Wakeup auto-reload value bits

When the wakeup timer is enabled (WUTE set to 1), the WUTF flag is set every (WUT[15:0]

+ 1) ck_wut cycles. The ck_wut period is selected through WUCKSEL[2:0] bits of the

RTC_CR register

When WUCKSEL[2] = 1, the wakeup timer becomes 17-bits and WUCKSEL[1] effectively

becomes WUT[16] the most-significant bit to be reloaded into the timer.

Note: The first assertion of WUTF occurs (WUT+1) ck_wut cycles after WUTE is set. Setting

WUT[15:0] to 0x0000 with WUCKSEL[2:0] =011 (RTCCLK/2) is forbidden.

Loading...

Loading...