Serial peripheral interface (SPI) RM0090

825/1422 Doc ID 018909 Rev 4

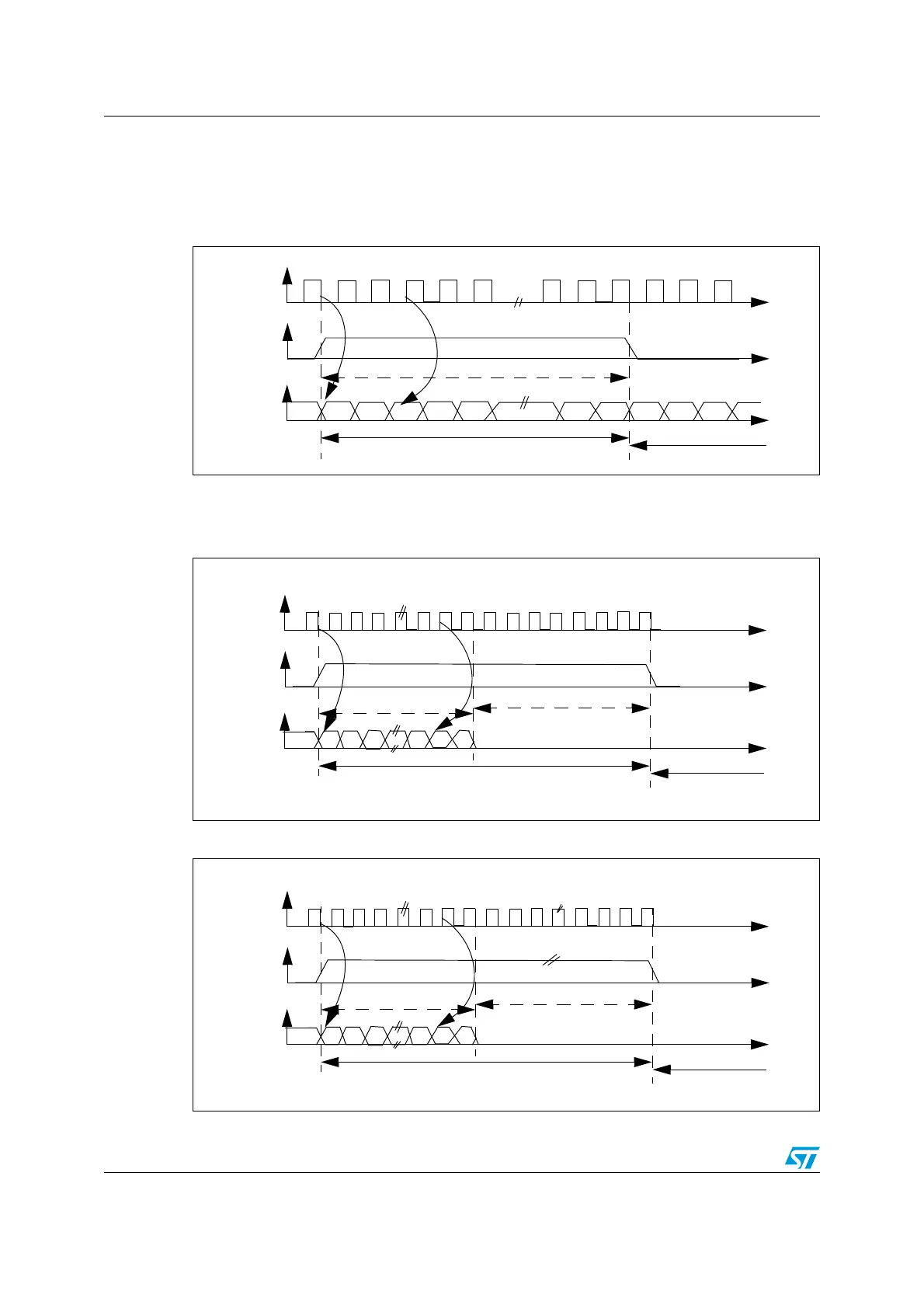

MSB justified standard

For this standard, the WS signal is generated at the same time as the first data bit, which is

the MSBit.

Figure 295. MSB Justified 16-bit or 32-bit full-accuracy length with CPOL = 0

Data are latched on the falling edge of CK (for transmitter) and are read on the rising edge

(for the receiver).

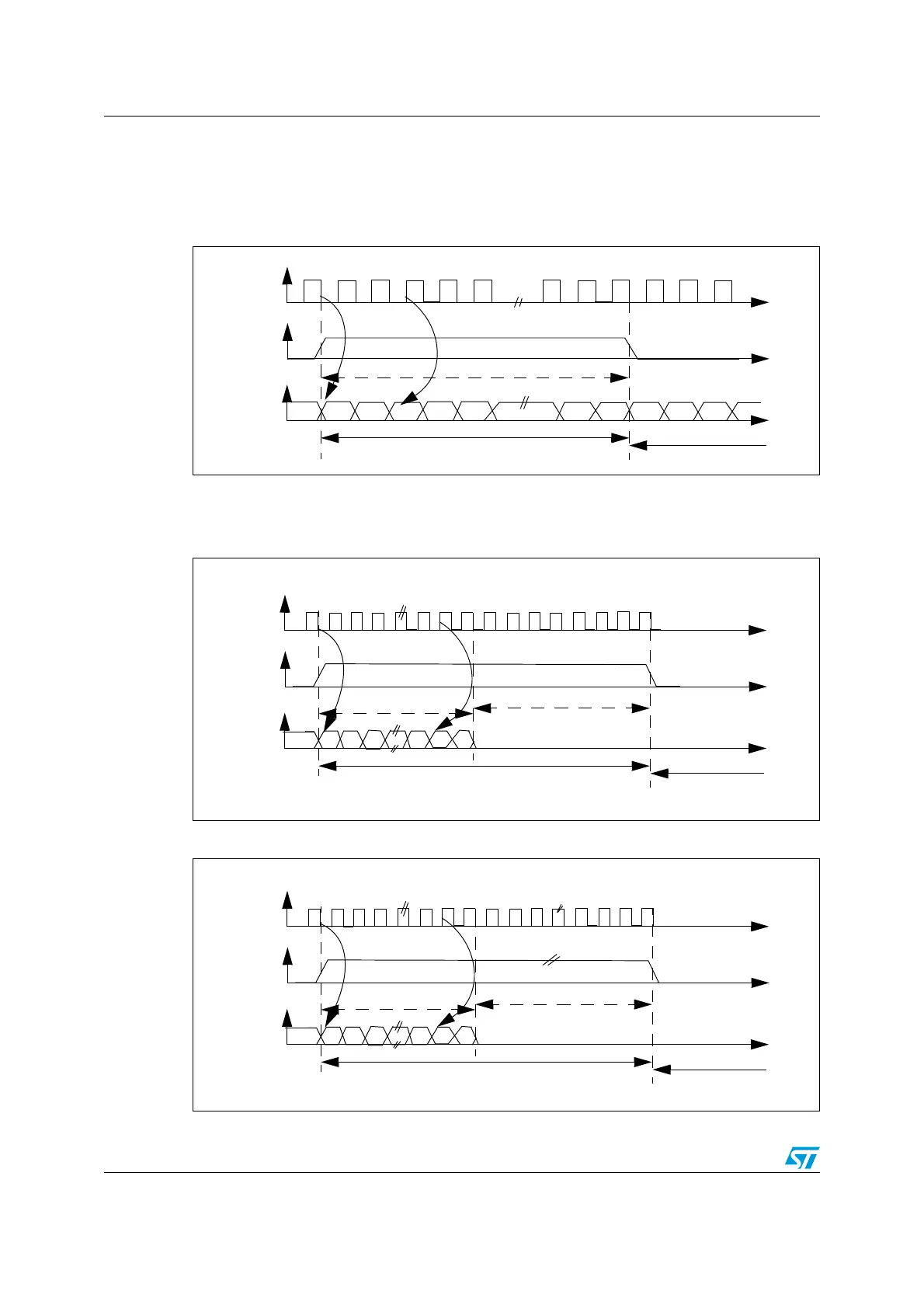

Figure 296. MSB Justified 24-bit frame length with CPOL = 0

Figure 297. MSB Justified 16-bit extended to 32-bit packet frame with CPOL = 0

MSB LSB MSB

CK

WS

SD

Channel left

Channel right

May be 16-bit, 32-bit

Transmission

Reception

CK

WS

SD

Channel left 32-bit

Channel right

MSB

LSB

8-bit remaining

0 forced

24-bit data

Transmission

Reception

CK

WS

SD

Channel left 32-bit

Channel right

MSB

LSB

16-bit remaining

0 forced

16-bit data

Transmission

Reception

Loading...

Loading...