DMA controller (DMA) RM0090

229/1422 Doc ID 018909 Rev 4

In all cases, the burst size multiplied by the data size must not exceed the FIFO size (data

size can be: 1 (byte), 2 (half-word) or 4 (word)).

Incomplete Burst transfer at the end of a DMA transfer may happen if one of the following

conditions occurs:

● For the AHB peripheral port configuration: the total number of data items (set in the

DMA_SxNDTR register) is not a multiple of the burst size multiplied by the data size

● For the AHB memory port configuration: the number of remaining data items in the

FIFO to be transferred to the memory is not a multiple of the burst size multiplied by the

data size

In such cases, the remaining data to be transferred will be managed in single mode by the

DMA, even if a burst transaction was requested during the DMA stream configuration.

Note: When burst transfers are requested on the peripheral AHB port and the FIFO is used

(DMDIS = 1 in the DMA_SxCR register), it is mandatory to respect the following rule to avoid

permanent underrun or overrun conditions, depending on the DMA stream direction:

If (PBURST × PSIZE) = FIFO_SIZE (4 words), FIFO_Threshold = 3/4 is forbidden with

PSIZE = 1, 2 or 4 and PBURST = 4, 8 or 16.

This rule ensures that enough FIFO space at a time will be free to serve the request from

the peripheral.

FIFO flush

The FIFO can be flushed when the stream is disabled by resetting the EN bit in the

DMA_SxCR register and when the stream is configured to manage peripheral-to-memory or

memory-to-memory transfers: If some data are still present in the FIFO when the stream is

disabled, the DMA controller continues transferring the remaining data to the destination

(even though stream is effectively disabled). When this flush is completed, the transfer

complete status bit (TCIFx) in the DMA_LISR or DMA_HISR register is set.

The remaining data counter DMA_SxNDTR keeps the value in this case to indicate how

many data items are currently available in the destination memory.

Note that during the FIFO flush operation, if the number of remaining data items in the FIFO

to be transferred to memory (in bytes) is less than the memory data width (for example 2

bytes in FIFO while MSIZE is configured to word), data will be sent with the data width set in

the MSIZE bit in the DMA_SxCR register. This means that memory will be written with an

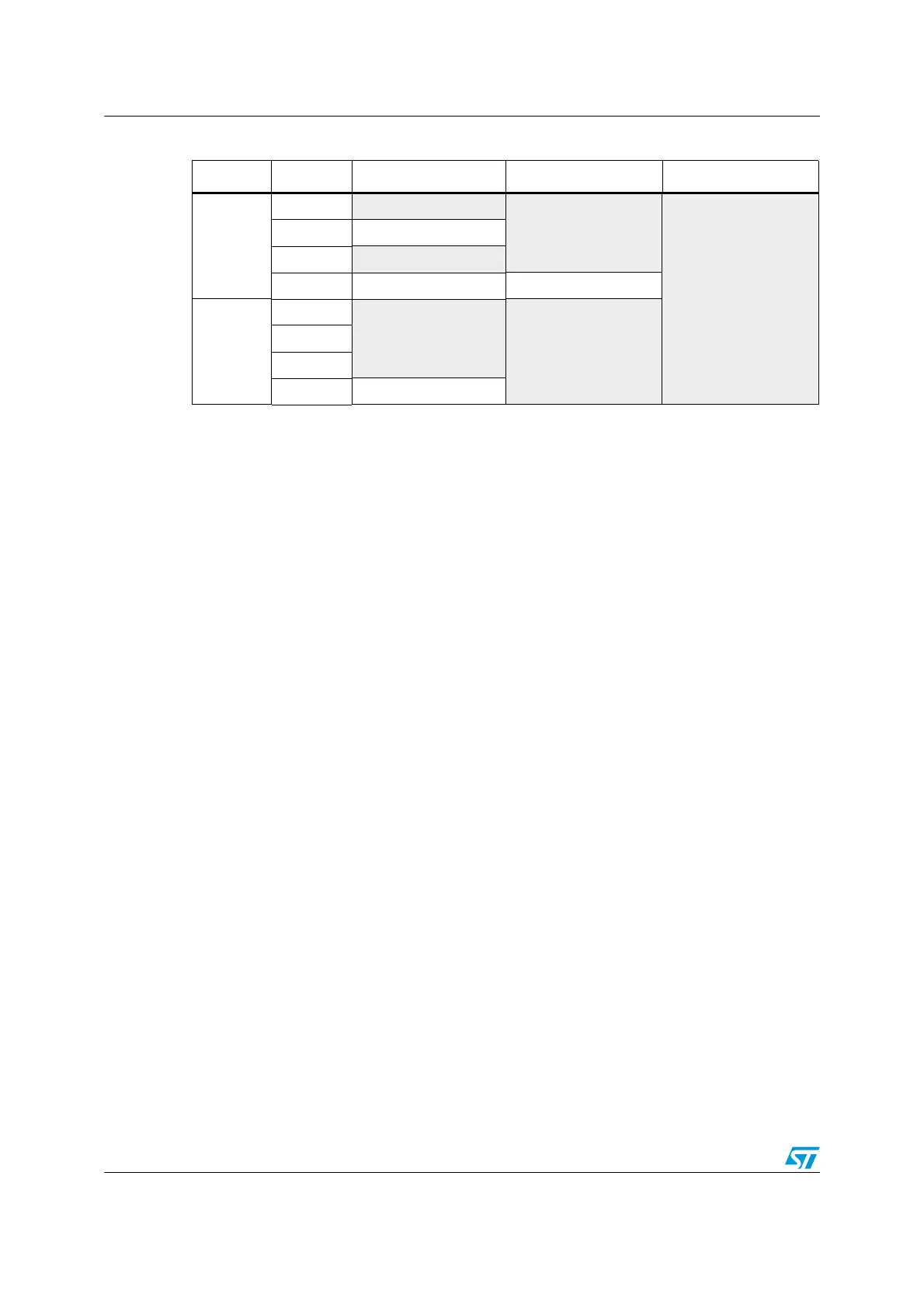

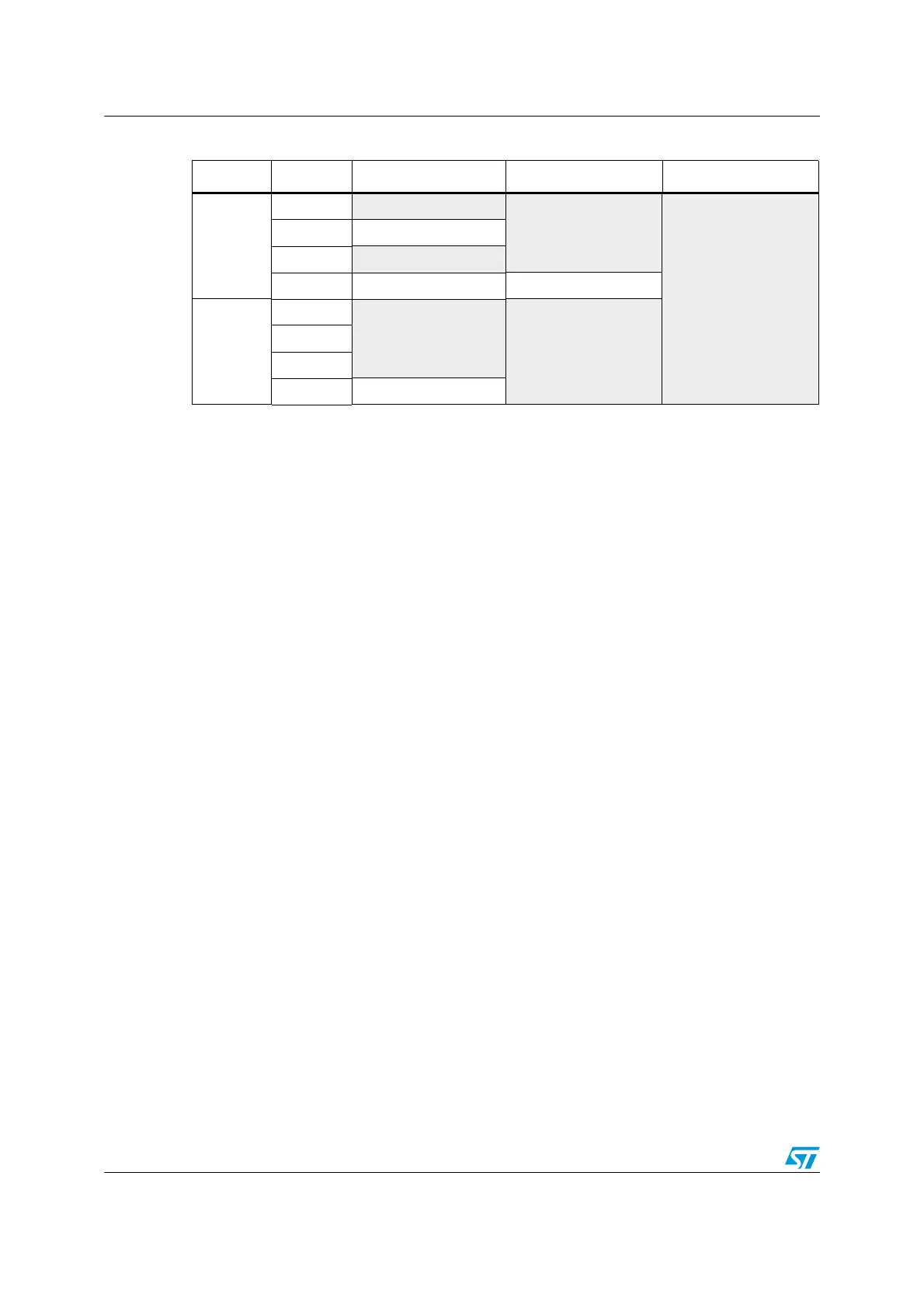

Half-word

1/4

forbidden

forbidden

forbidden

1/2 1 burst of 4 beats

3/4

forbidden

Full 2 bursts of 4 beats 1 burst of 8 beats

Word

1/4

forbidden

forbidden

1/2

3/4

Full 1 burst of 4 beats

Table 41. FIFO threshold configurations (continued)

MSIZE FIFO level MBURST = INCR4 MBURST = INCR8 MBURST = INCR16

Loading...

Loading...