RM0090 USB on-the-go full-speed (OTG_FS)

Doc ID 018909 Rev 4 1036/1422

FIFO and queue status register (HNPTXSTS) are read-only registers which can be used by

the application to read the status of each request queue. They contain:

● The number of free entries currently available in the periodic (nonperiodic) request

queue (8 max)

● Free space currently available in the periodic (nonperiodic) Tx-FIFO (out-transactions)

● IN/OUT token, host channel number and other status information.

As request queues can hold a maximum of 8 entries each, the application can push to

schedule host transactions in advance with respect to the moment they physically reach the

SB for a maximum of 8 pending periodic transactions plus 8 pending nonperiodic

transactions.

To post a transaction request to the host scheduler (queue) the application must check that

there is at least 1 entry available in the periodic (nonperiodic) request queue by reading the

PTXQSAV bits in the OTG_FS_HNPTXSTS register or NPTQXSAV bits in the

OTG_FS_HNPTXSTS register.

30.7 SOF trigger

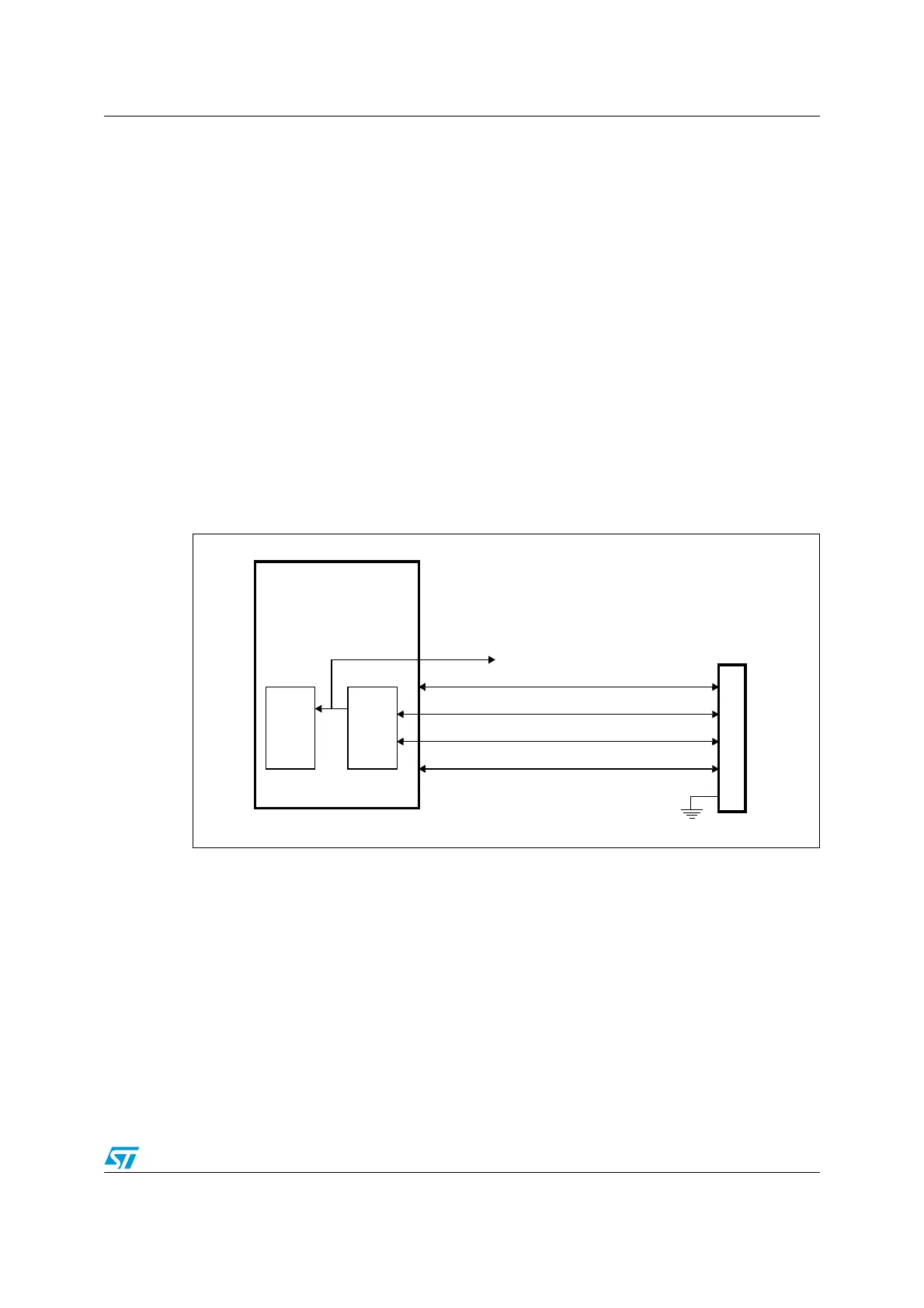

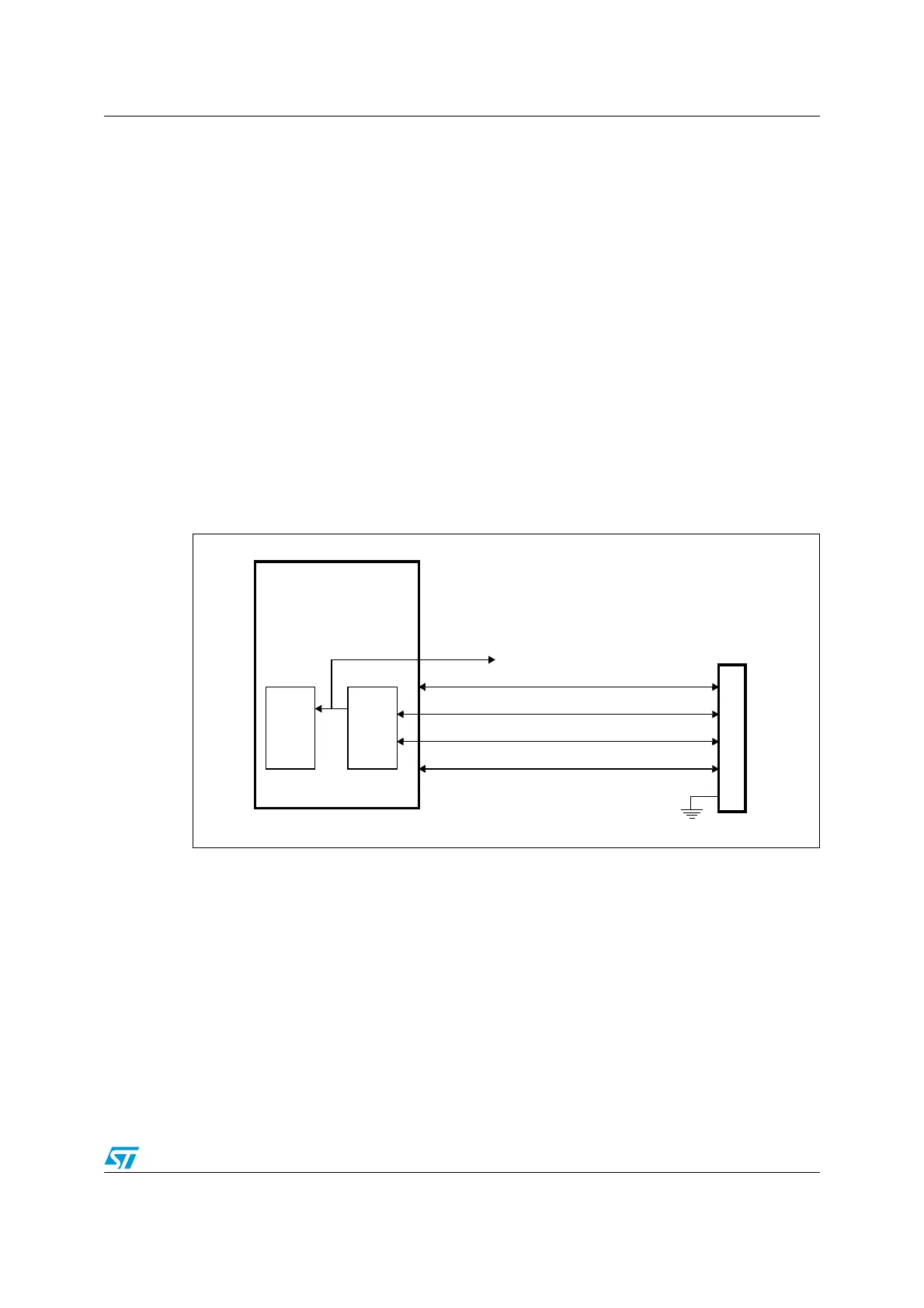

Figure 361. SOF connectivity

The OTG FS core provides means to monitor, track and configure SOF framing in the host

and peripheral, as well as an SOF pulse output connectivity feature.

Such utilities are especially useful for adaptive audio clock generation techniques, where the

audio peripheral needs to synchronize to the isochronous stream provided by the PC, or the

host needs to trim its framing rate according to the requirements of the audio peripheral.

30.7.1 Host SOFs

In host mode the number of PHY clocks occurring between the generation of two

consecutive SOF (FS) or Keep-alive (LS) tokens is programmable in the host frame interval

register (HFIR), thus providing application control over the SOF framing period. An interrupt

is generated at any start of frame (SOF bit in OTH_FS_GINTSTS). The current frame

STM32F4xx

STM32F4xx

VBUS

D

+

V

SS

PA8

PA1 2

PA1 1

USB mic ro-AB connector

D

-

IDTIM2

ITR1 SOF

pulse

SOFgen

PA9

PA1 0

SOF pulse output, to

external audio control

MS19907V2

Loading...

Loading...