Interrupts and events RM0090

257/1422 Doc ID 018909 Rev 4

10.2.1 EXTI main features

The main features of the EXTI controller are the following:

● independent trigger and mask on each interrupt/event line

● dedicated status bit for each interrupt line

● generation of up to 23 software event/interrupt requests

● detection of external signals with a pulse width lower than the APB2 clock period. Refer

to the electrical characteristics section of the STM32F4xx datasheets for details on this

parameter.

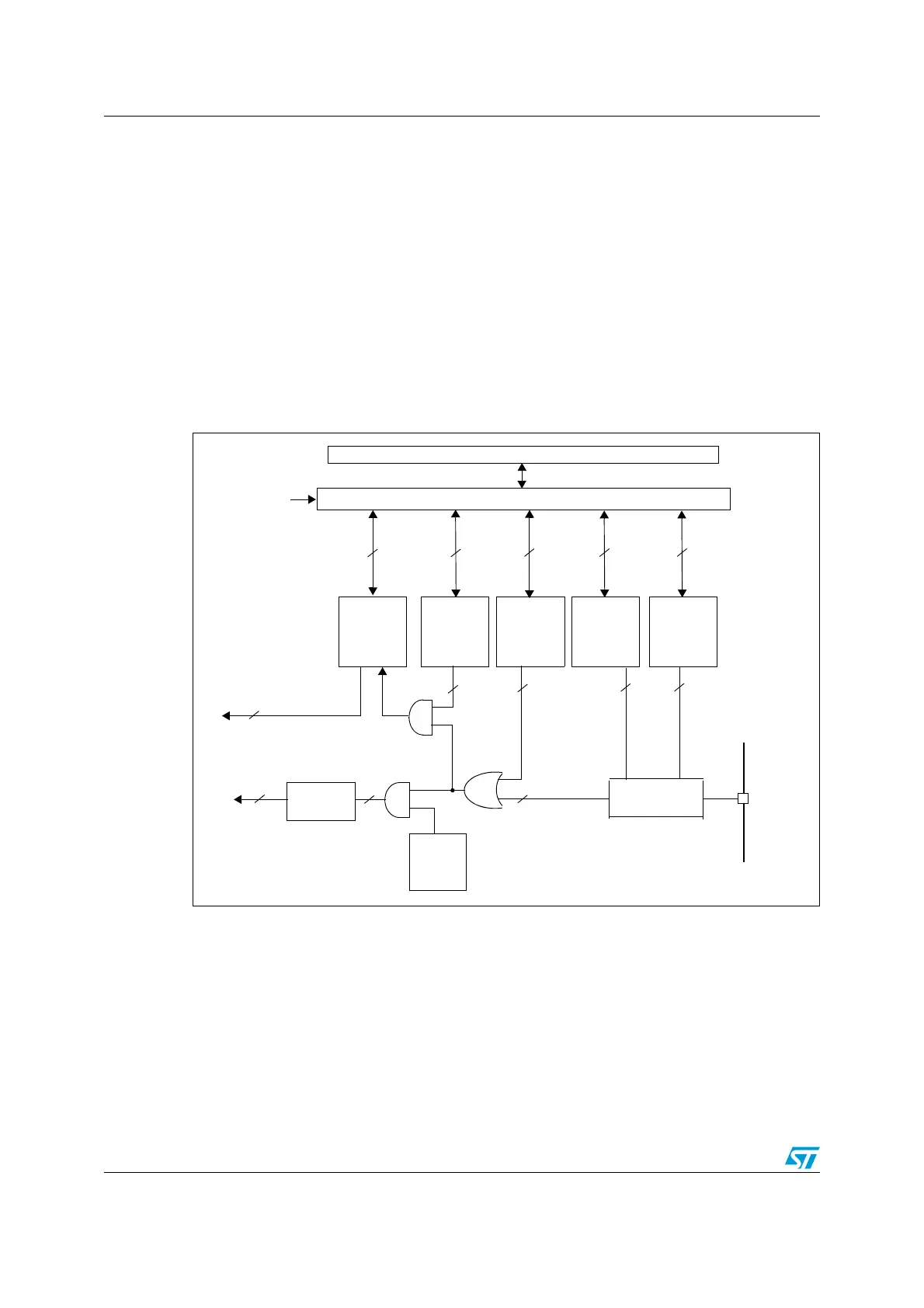

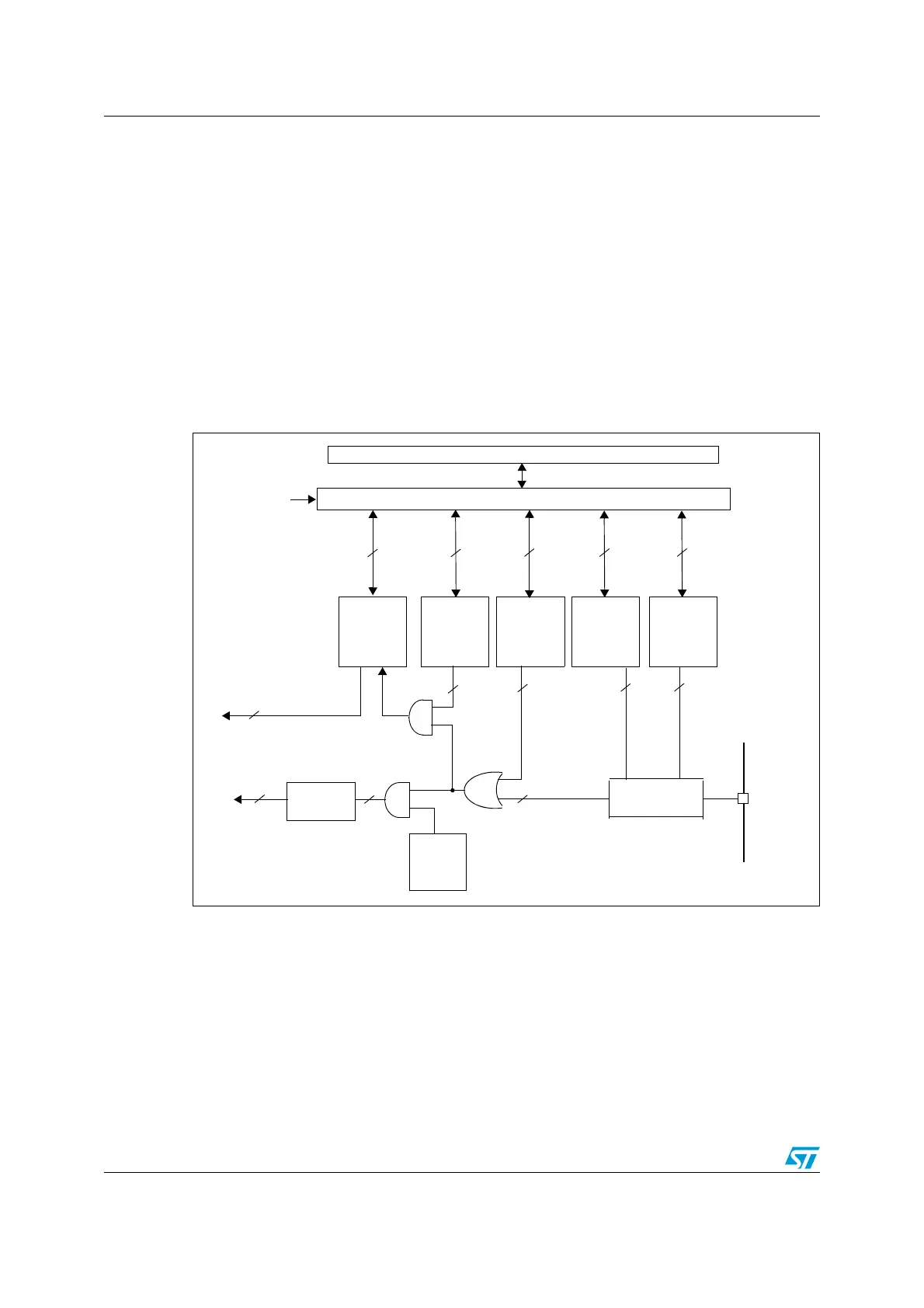

10.2.2 EXTI block diagram

Figure 32 shows the block diagram.

Figure 32. External interrupt/event controller block diagram

10.2.3 Wakeup event management

The STM32F4xx are able to handle external or internal events in order to wake up the core

(WFE). The wakeup event can be generated either by:

● enabling an interrupt in the peripheral control register but not in the NVIC, and enabling

the SEVONPEND bit in the Cortex™-M4F System Control register. When the MCU

Peripheral interface

Edge detect

circuit

AMBA APB bus

PCLK2

23

23 23

2323

23

23

To NVIC interrupt

controller

Software

interrupt

event

Register

Rising

trigger

selection

regsiter

23

Event

mask

register

Pulse

generator

23

23

23

23

Input

line

Pending

request

register

23

ai15896b

Interrupt

mask

register

Falling

trigger

selection

regsiter

Loading...

Loading...