Hash processor (HASH) RM0090

609/1422 Doc ID 018909 Rev 4

register), the HASH_CSR22 to HASH_CSR37 registers do not have to be saved and

restored.

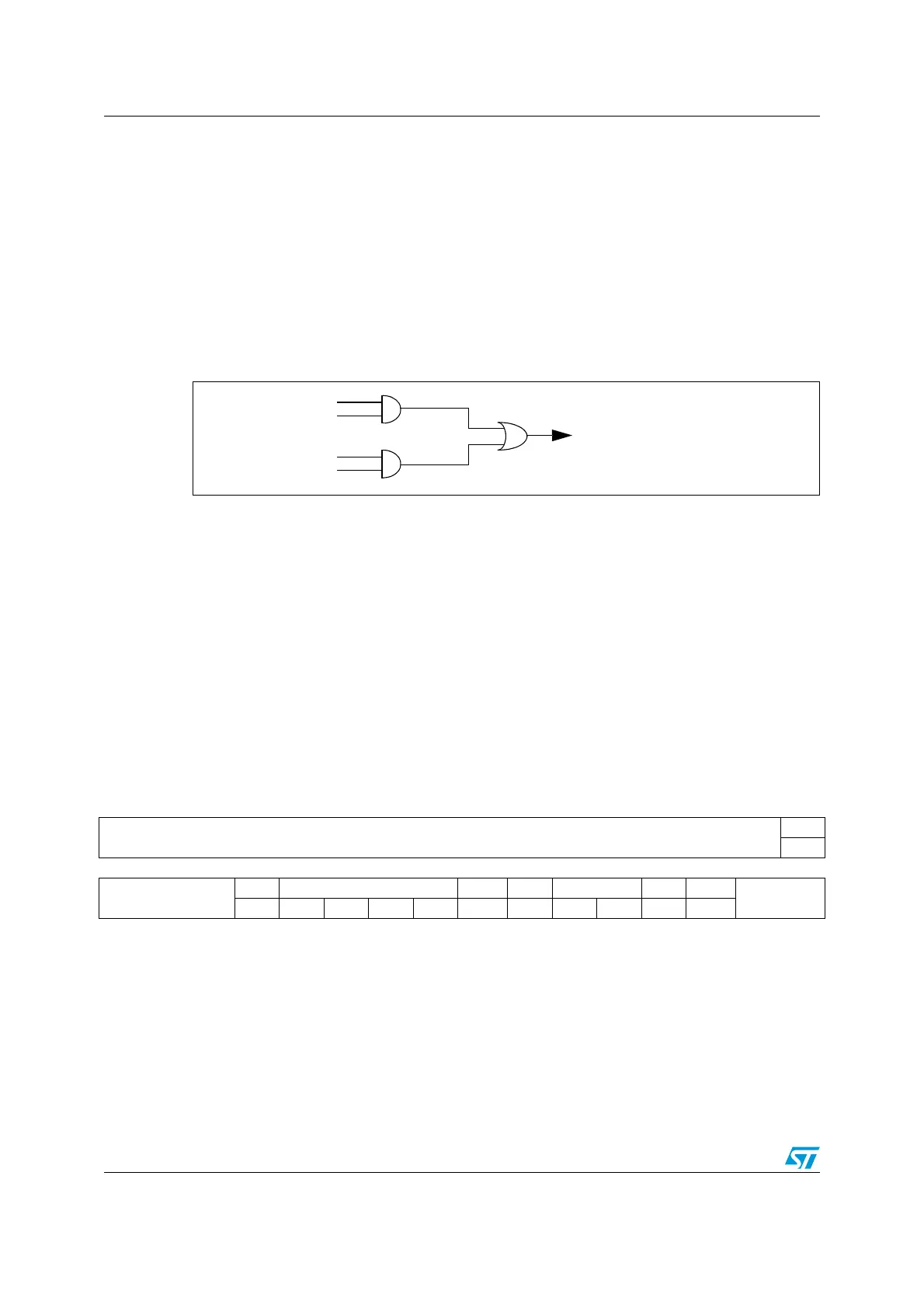

22.3.8 HASH interrupt

There are two individual maskable interrupt sources generated by the HASH processor.

They are connected to the same interrupt vector.

You can enable or disable the interrupt sources individually by changing the mask bits in the

HASH_IMR register. Setting the appropriate mask bit to 1 enables the interrupt.

The status of the individual interrupt sources can be read from the HASH_SR register.

Figure 221. HASH interrupt mapping diagram

22.4 HASH registers

The HASH core is associated with several control and status registers and five message

digest registers.

All these registers are accessible through word accesses only, else an AHB error is

generated.

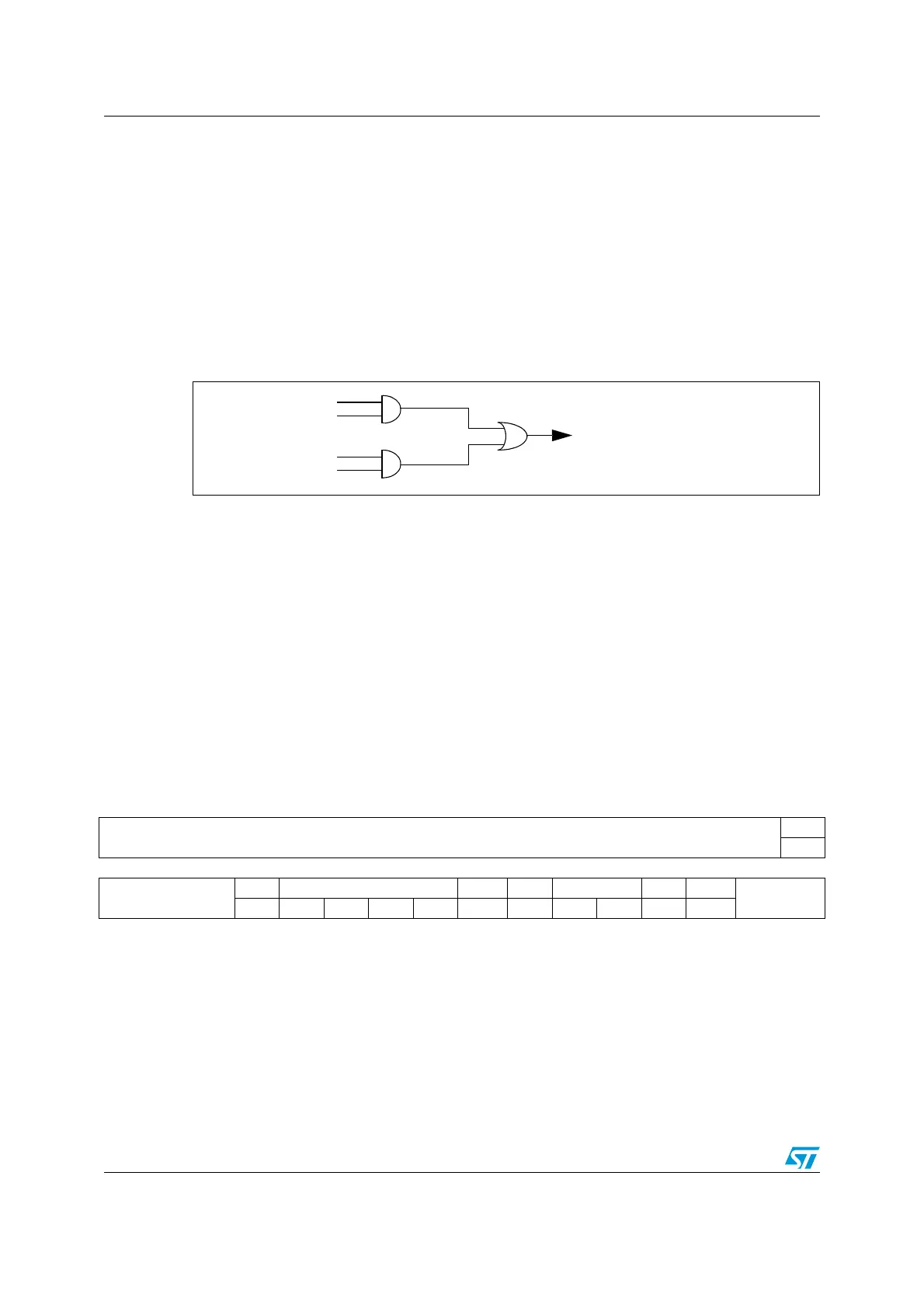

22.4.1 HASH control register (HASH_CR) for

STM32F405xx/07xx and STM32F415xx/17xx

Address offset: 0x00

Reset value: 0x0000 0000

DCIS

DCIM

DINIS

DINIM

HASH interrupt to NVIC

ai16086

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

LKEY

rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

DINNE NBW ALGO[0] MODE DATATYPE DMAE INIT

Reserved

rrrrrrwrwrwrwrww

Loading...

Loading...