Analog-to-digital converter (ADC) RM0090

275/1422 Doc ID 018909 Rev 4

Software source trigger events can be generated by setting SWSTART (for regular

conversion) or JSWSTART (for injected conversion) in ADC_CR2.

A regular group conversion can be interrupted by an injected trigger.

Note: The trigger selection can be changed on the fly. However, when the selection changes, there

is a time frame of 1 APB clock cycle during which the trigger detection is disabled. This is to

avoid spurious detection during transitions.

11.7 Fast conversion mode

It is possible to perform faster conversion by reducing the ADC resolution. The RES bits are

used to select the number of bits available in the data register. The minimum conversion

time for each resolution is then as follows:

● 12 bits: 3 + 12 = 15 ADCCLK cycles

● 10 bits: 3 + 10 = 13 ADCCLK cycles

● 8 bits: 3 + 8 = 11 ADCCLK cycles

● 6 bits: 3 + 6 = 9 ADCCLK cycles

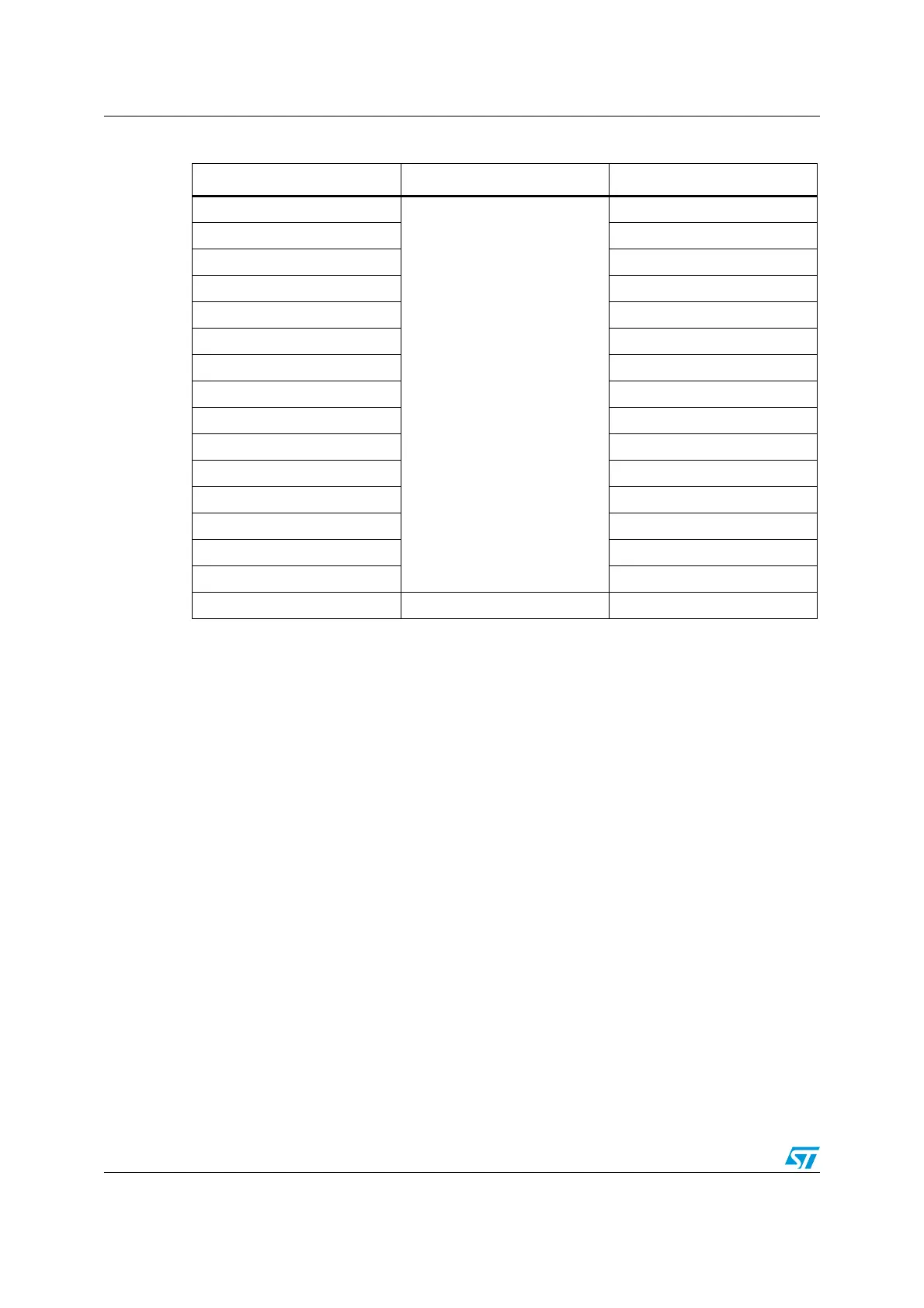

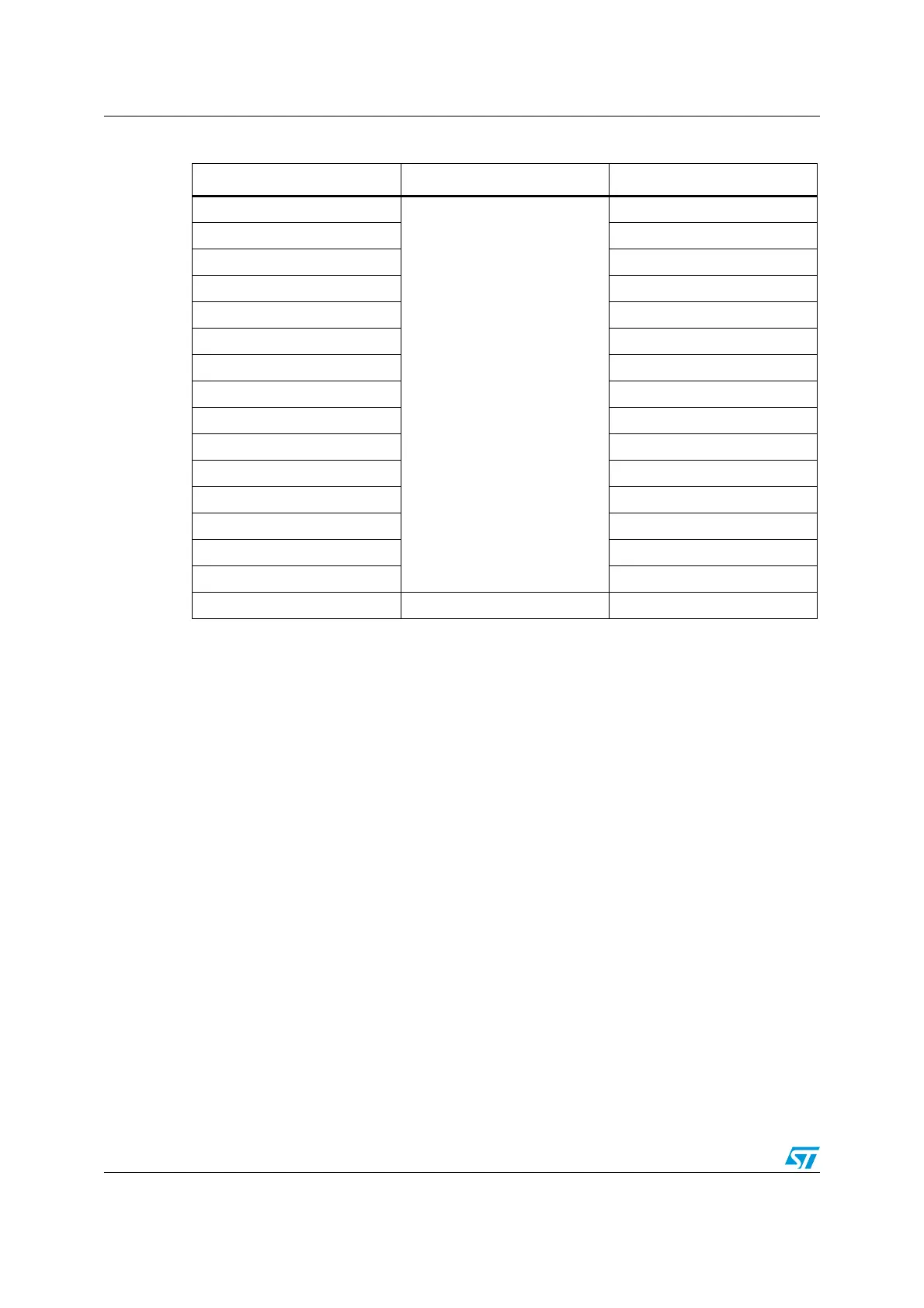

Table 52. External trigger for injected channels

Source Connection type JEXTSEL[3:0]

TIM1_CH4 event

Internal signal from on-chip

timers

0000

TIM1_TRGO event 0001

TIM2_CH1 event 0010

TIM2_TRGO event 0011

TIM3_CH2 event 0100

TIM3_CH4 event 0101

TIM4_CH1 event 0110

TIM4_CH2 event 0111

TIM4_CH3 event 1000

TIM4_TRGO event 1001

TIM5_CH4 event 1010

TIM5_TRGO event 1011

TIM8_CH2 event 1100

TIM8_CH3 event 1101

TIM8_CH4 event 1110

EXTI line15 External pin 1111

Loading...

Loading...