RM0090 Serial peripheral interface (SPI)

Doc ID 018909 Rev 4 826/1422

LSB justified standard

This standard is similar to the MSB justified standard (no difference for the 16-bit and 32-bit

full-accuracy frame formats).

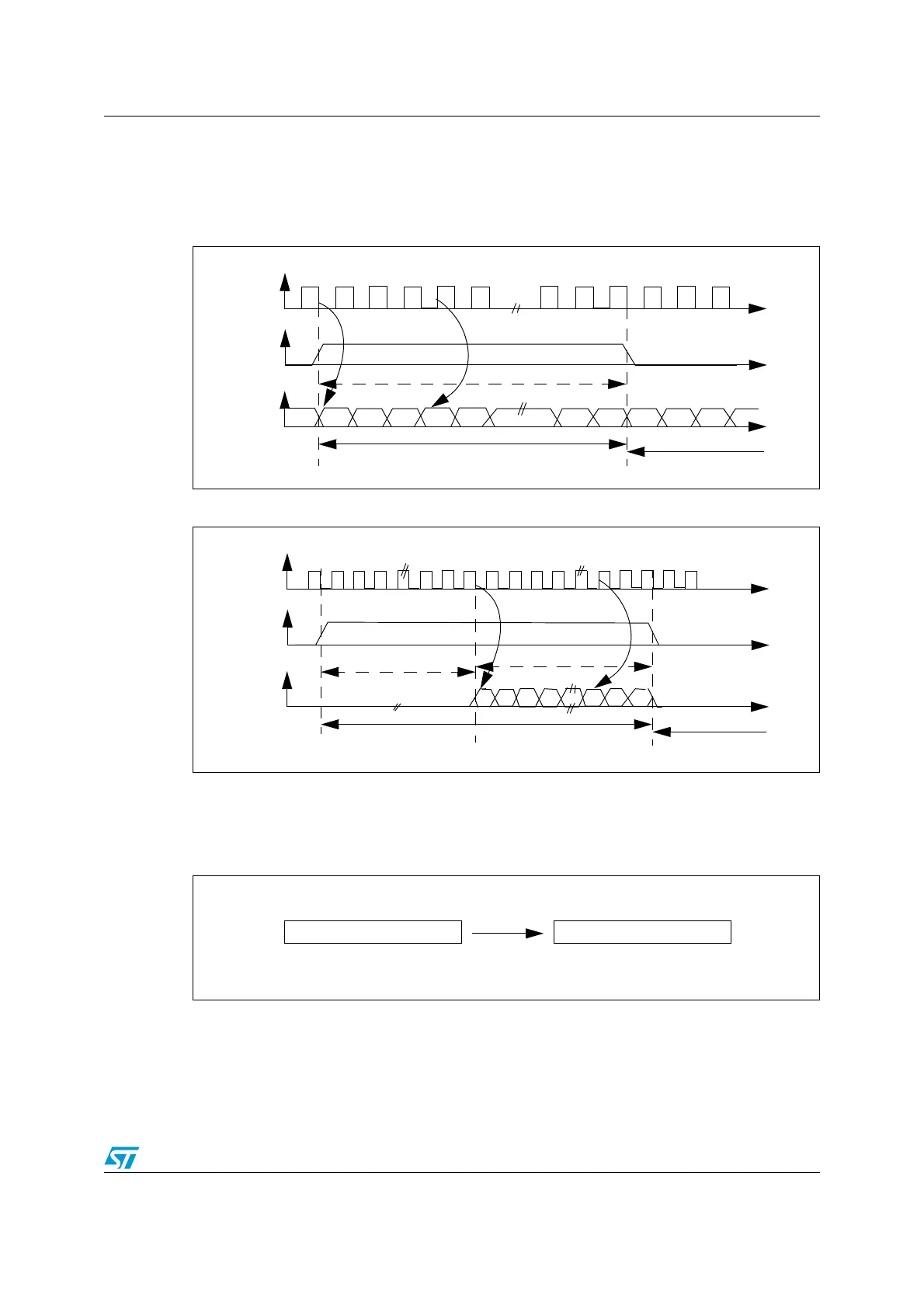

Figure 298. LSB justified 16-bit or 32-bit full-accuracy with CPOL = 0

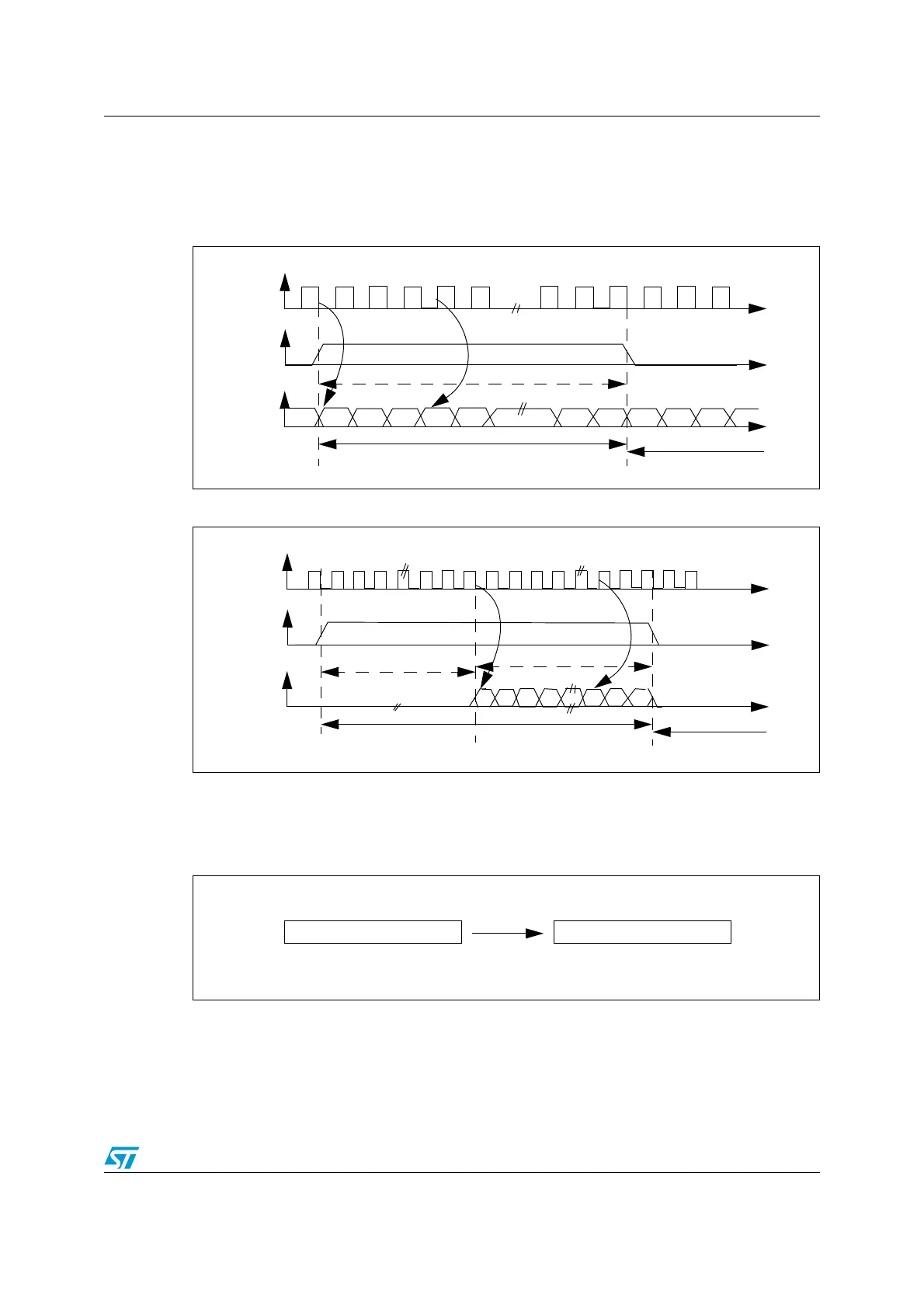

Figure 299. LSB Justified 24-bit frame length with CPOL = 0

● In transmission mode:

If data 0x3478AE have to be transmitted, two write operations to the SPI_DR register

are required from software or by DMA. The operations are shown below.

Figure 300. Operations required to transmit 0x3478AE

● In reception mode:

If data 0x3478AE are received, two successive read operations from SPI_DR are

required on each RXNE event.

MSB LSB MSB

CK

WS

SD

Channel left

Channel right

May be 16-bit, 32-bit

Transmission

Reception

CK

WS

SD

Channel left 32-bit

Channel right

MSB

LSB

24-bit remaining

0 forced

8-bit data

Transmission

Reception

0xXX34 0x78AE

First write to Data register

Second write to Data register

Only the 8 LSB bits of the half-word

are significant. Whatever the 8 MSBs

a field of 0x00 is forced instead

conditioned by TXE = ‘1’

conditioned by TXE = ‘1’

Loading...

Loading...