RM0090 Power controller (PWR)

Doc ID 018909 Rev 4 108/1422

5.4.3 PWR power control/status register (PWR_CSR)

Address offset: 0x04

Reset value: 0x0000 0000 (not reset by wakeup from Standby mode)

Additional APB cycles are needed to read this register versus a standard APB read.

Bit 3 CSBF: Clear standby flag

This bit is always read as 0.

0: No effect

1: Clear the SBF Standby Flag (write).

Bit 2 CWUF: Clear wakeup flag

This bit is always read as 0.

0: No effect

1: Clear the WUF Wakeup Flag after 2 System clock cycles

Bit 1 PDDS: Power-down deepsleep

This bit is set and cleared by software. It works together with the LPDS bit.

0: Enter Stop mode when the CPU enters deepsleep. The regulator status depends on the

LPDS bit.

1: Enter Standby mode when the CPU enters deepsleep.

Bit 0 LPDS: Low-power deepsleep

This bit is set and cleared by software. It works together with the PDDS bit.

0: Voltage regulator on during Stop mode

1: Voltage regulator in low-power mode during Stop mode

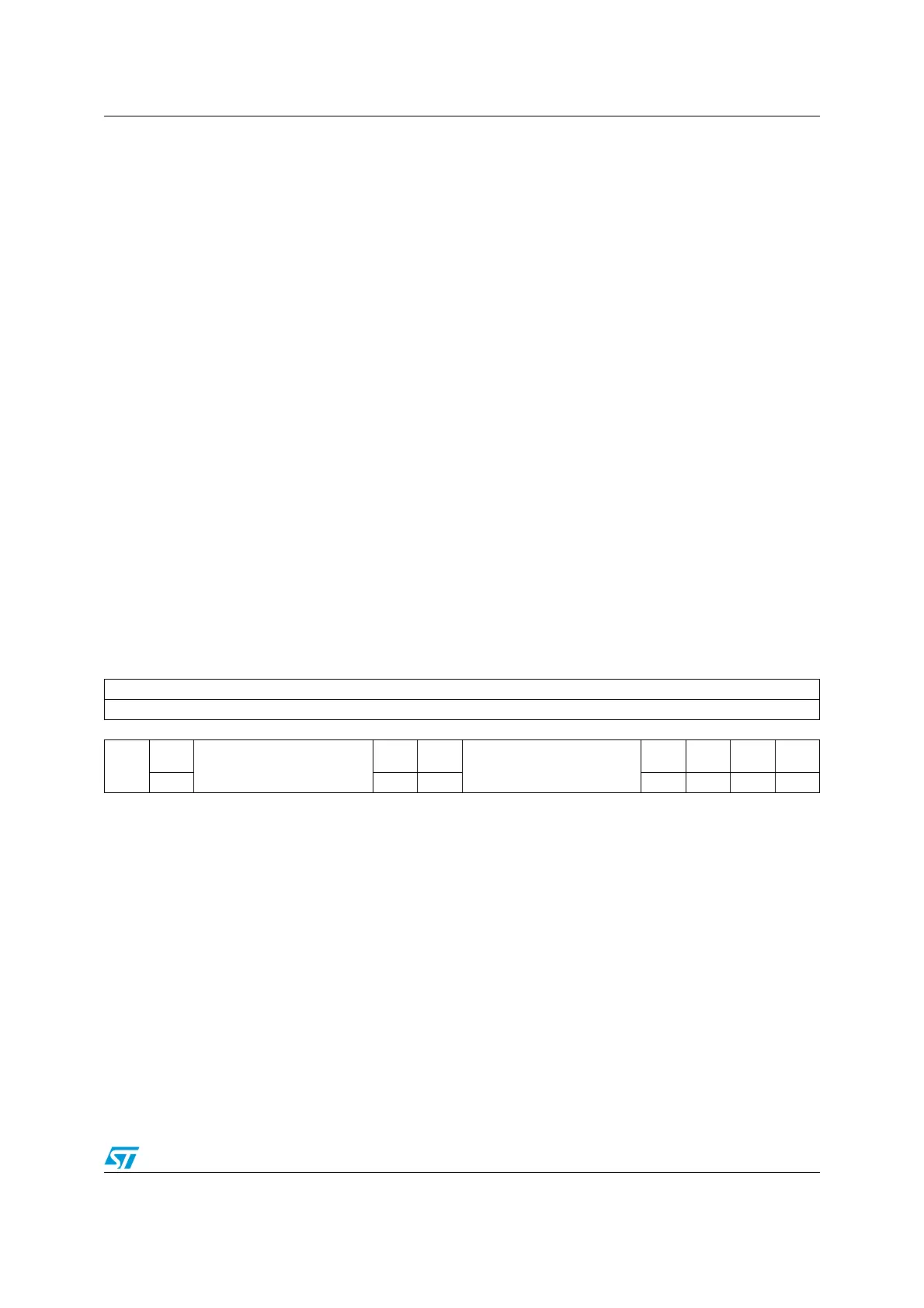

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

Res.

1514131211109876543210

Res

VOS

RDY

Reserved

BRE EWUP

Reserved

Res.

BRR PVDO SBF WUF

r rwrw rrrr

Bits 31:15 Reserved, must be kept at reset value.

Bit 14 VOSRDY: Regulator voltage scaling output selection ready bit

0: Not ready

1: Ready

Bits 13:10 Reserved, must be kept at reset value.

Bit 9 BRE: Backup regulator enable

When set, the Backup regulator (used to maintain backup SRAM content in Standby and

V

BAT

modes) is enabled. If BRE is reset, the backup regulator is switched off. The backup

SRAM can still be used but its content will be lost in the Standby and V

BAT

modes. Once set,

the application must wait that the Backup Regulator Ready flag (BRR) is set to indicate that

the data written into the RAM will be maintained in the Standby and V

BAT

modes.

0: Backup regulator disabled

1: Backup regulator enabled

Note: This bit is not reset when the device wakes up from Standby mode, by a system reset,

or by a power reset.

Loading...

Loading...