RM0090 Real-time clock (RTC)

Doc ID 018909 Rev 4 646/1422

Note: WUT = Wakeup unit counter value. WUT = (0x0000 to 0xFFFF) + 0x10000 added when

WUCKSEL[2:1 = 11].

Bits 7, 6 and 4 of this register can be written in initialization mode only (RTC_ISR/INITF = 1).

Bits 2 to 0 of this register can be written only when RTC_CR WUTE bit = 0 and RTC_ISR

WUTWF bit = 1.

It is recommended not to change the hour during the calendar hour increment as it could

mask the incrementation of the calendar hour.

ADD1H and SUB1H changes are effective in the next second.

This register is write protected. The write access procedure is described in RTC register

write protection on page 630.

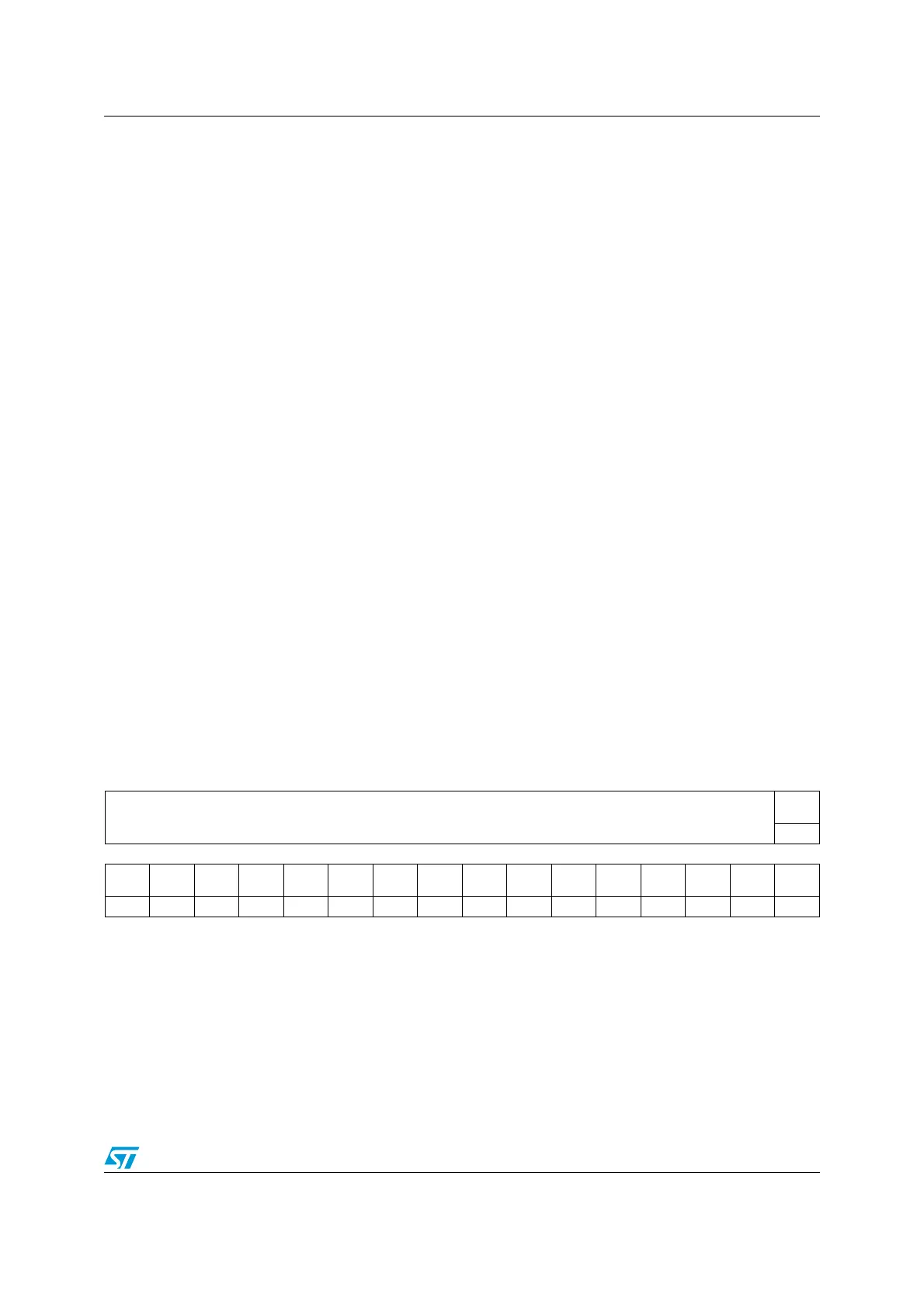

23.6.4 RTC initialization and status register (RTC_ISR)

Address offset: 0x0C

Power-on reset value: 0x0000 0007

System reset value: Not affected except INIT, INITF and RSF which are cleared to 0.

Bit 3 TSEDGE: Timestamp event active edge

0: TIMESTAMP rising edge generates a timestamp event

1: TIMESTAMP falling edge generates a timestamp event

TSE must be reset when TSEDGE is changed to avoid unwanted TSF setting

Bits 2:0 WUCKSEL[2:0]: Wakeup clock selection

000: RTC/16 clock is selected

001: RTC/8 clock is selected

010: RTC/4 clock is selected

011: RTC/2 clock is selected

10x: ck_spre (usually 1 Hz) clock is selected

11x: ck_spre (usually 1 Hz) clock is selected and 2

16

is added to the WUT counter value

(see note below)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

RECAL

PF

r

1514131211109876543210

Res.

TA MP

2F

TA MP

1F

TSOVF TSF WUTF ALRBF ALRAF INIT INITF RSF INITS SHPF

WUT

WF

ALRB

WF

ALRA

WF

rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rw r rc_w0 r rc_w0 r r r

Bits 31:17 Reserved

Bit 16 RECALPF: Recalibration pending Flag

The RECALPF status flag is automatically set to ‘1’ when software writes to the RTC_CALR

register, indicating that the RTC_CALR register is blocked. When the new calibration

settings are taken into account, this bit returns to ‘0’. Refer to Section : Re-calibration on-the-

fly.

Bit 15 Reserved, must be kept at reset value.

Loading...

Loading...