RM0090 DMA controller (DMA)

Doc ID 018909 Rev 4 244/1422

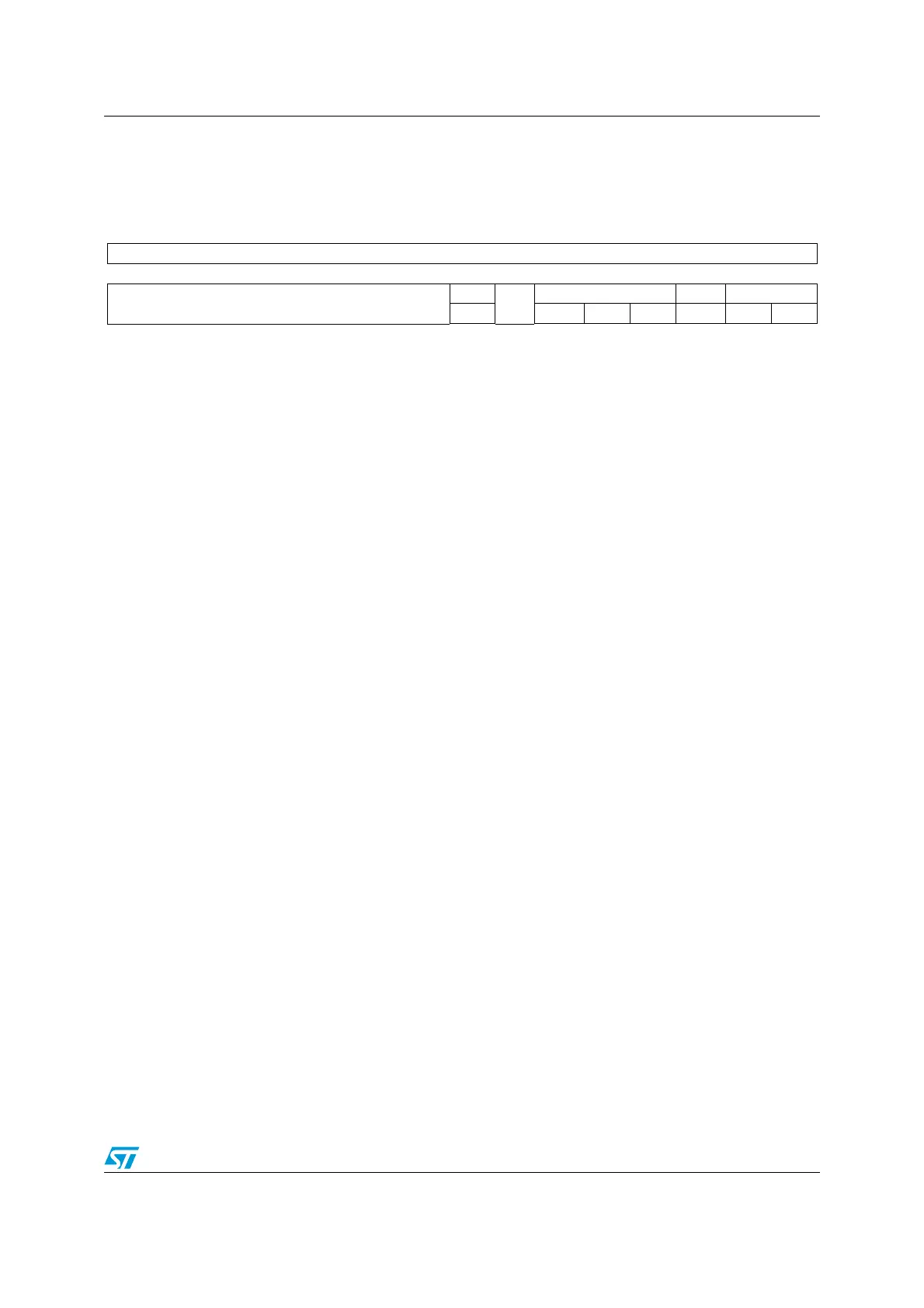

9.5.10 DMA stream x FIFO control register (DMA_SxFCR) (x = 0..7)

Address offset: 0x24 + 0x24 × stream number

Reset value: 0x0000 0021

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

FEIE

Reser

ved

FS[2:0] DMDIS FTH[1:0]

rw r r r rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7 FEIE: FIFO error interrupt enable

This bit is set and cleared by software.

0: FE interrupt disabled

1: FE interrupt enabled

Bits 6 Reserved, must be kept at reset value.

Bits 5:3 FS[2:0]: FIFO status

These bits are read-only.

000: 0 < fifo_level < 1/4

001: 1/4 ≤ fifo_level < 1/2

010: 1/2 ≤ fifo_level < 3/4

011: 3/4 ≤ fifo_level < full

100: FIFO is empty

101: FIFO is full

others: no meaning

These bits are not relevant in the direct mode (DMDIS bit is zero).

Bits 2 DMDIS: Direct mode disable

This bit is set and cleared by software. It can be set by hardware.

0: Direct mode enabled

1: Direct mode disabled

This bit is protected and can be written only if EN is ‘0’.

This bit is set by hardware if the memory-to-memory mode is selected (DIR bit in

DMA_SxCR are “10”) and the EN bit in the DMA_SxCR register is ‘1’ because the direct

mode is not allowed in the memory-to-memory configuration.

Bits 1:0 FTH[1:0]: FIFO threshold selection

These bits are set and cleared by software.

00: 1/4 full FIFO

01: 1/2 full FIFO

10: 3/4 full FIFO

11: full FIFO

These bits are not used in the direct mode when the DMIS value is zero.

These bits are protected and can be written only if EN is ‘1’.

Loading...

Loading...