RM0090 Real-time clock (RTC)

Doc ID 018909 Rev 4 656/1422

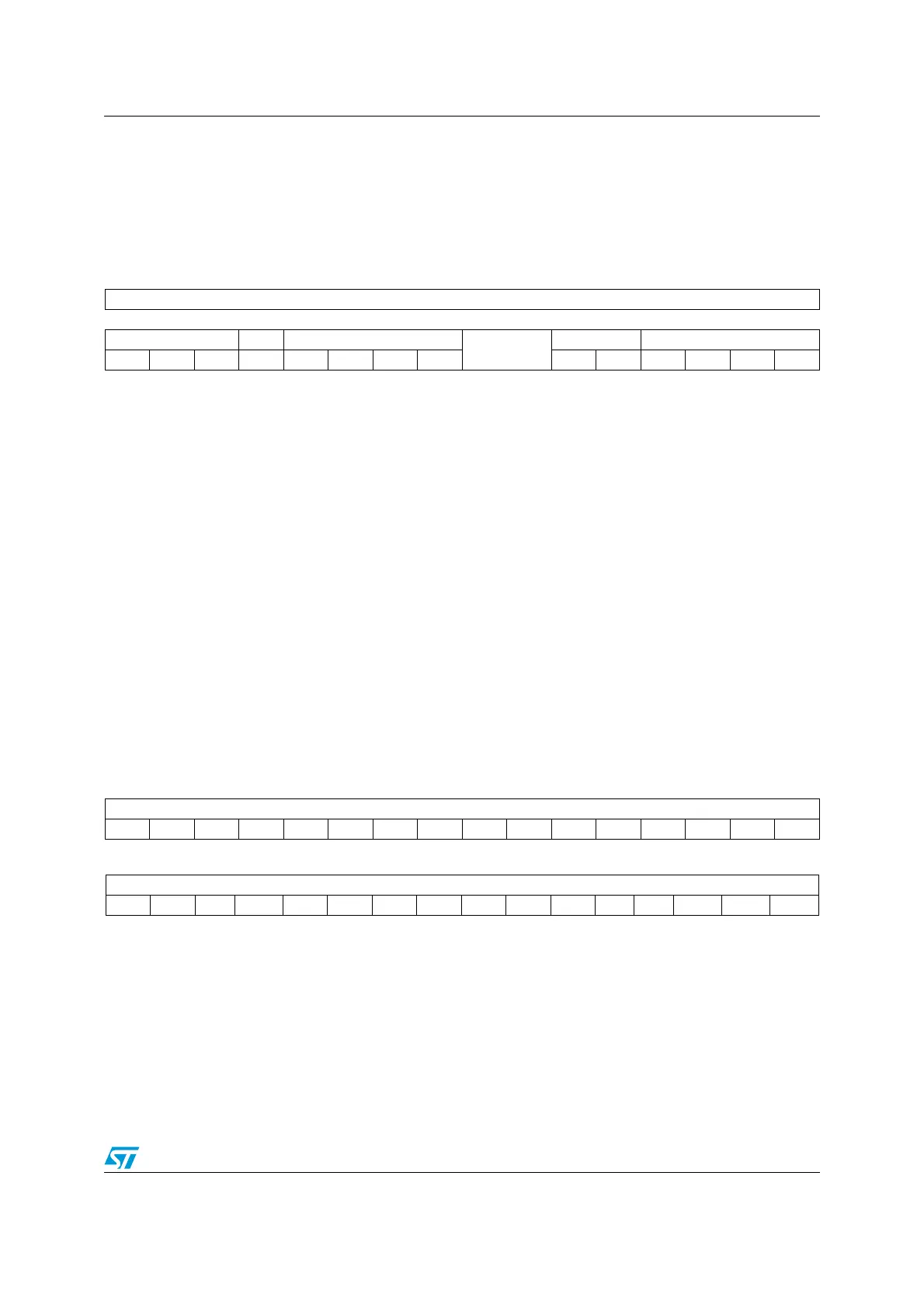

23.6.14 RTC time stamp date register (RTC_TSDR)

Address offset: 0x34

Power-on reset value: 0x0000 0000

System reset: not affected

Note: The content of this register is valid only when TSF is set to 1 in RTC_ISR. It is cleared when

TSF bit is reset.

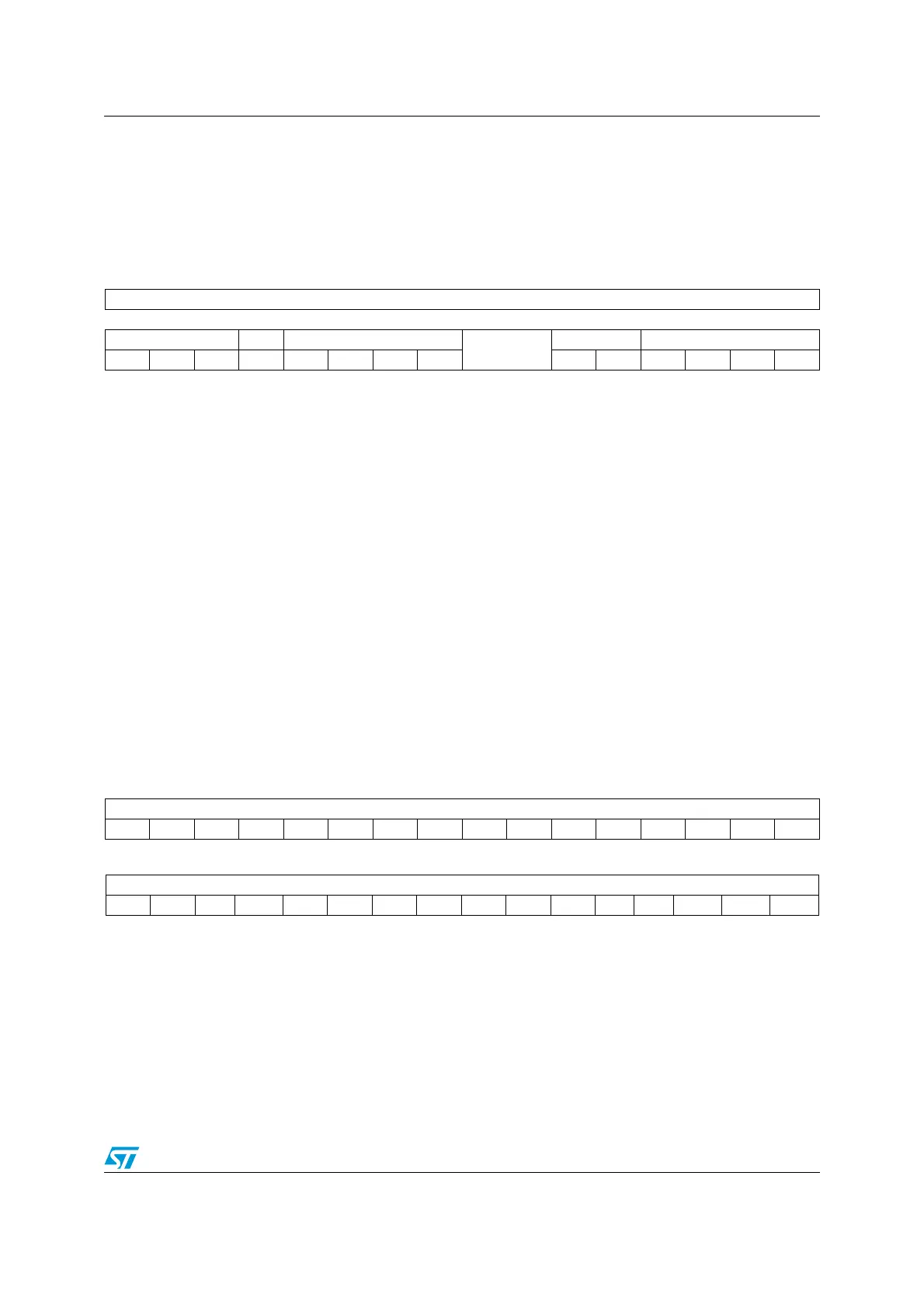

23.6.15 RTC timestamp sub second register (RTC_TSSSR)

Address offset: 0x38

Power-on reset value: 0x0000 0000

System reset: not affected

Note: The content of this register is valid only when RTC_ISR/TSF is set. It is cleared when the

RTC_ISR/TSF bit is reset.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

WDU[1:0] MT MU[3:0]

Reserved

DT[1:0] DU[3:0]

rrrrrrrr rrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:13 WDU[1:0]: Week day units

Bit 12 MT: Month tens in BCD format

Bits 11:8 MU[3:0]: Month units in BCD format

Bits 7:6 Reserved, must be kept at reset value.

Bits 5:4 DT[1:0]: Date tens in BCD format

Bit 3:0 DU[3:0]: Date units in BCD format

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

rrrrrrrrrrrrrrrr

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SS[15:0]

rrrr rrrrrrrrrr r r

Bits 31:16 Reserved

Bits 15:0 SS: Sub second value

SS[15:0] is the value of the synchronous prescaler’s counter when the timestamp event

occurred.

Loading...

Loading...