RM0090 Inter-integrated circuit (I

2

C) interface

Doc ID 018909 Rev 4 726/1422

25.4 I

2

C interrupts

The table below gives the list of I

2

C interrupt requests.

T

Note: SB, ADDR, ADD10, STOPF, BTF, RxNE and TxE are logically ORed on the same interrupt

channel.

BERR, ARLO, AF, OVR, PECERR, TIMEOUT and SMBALERT are logically ORed on the

same interrupt channel.

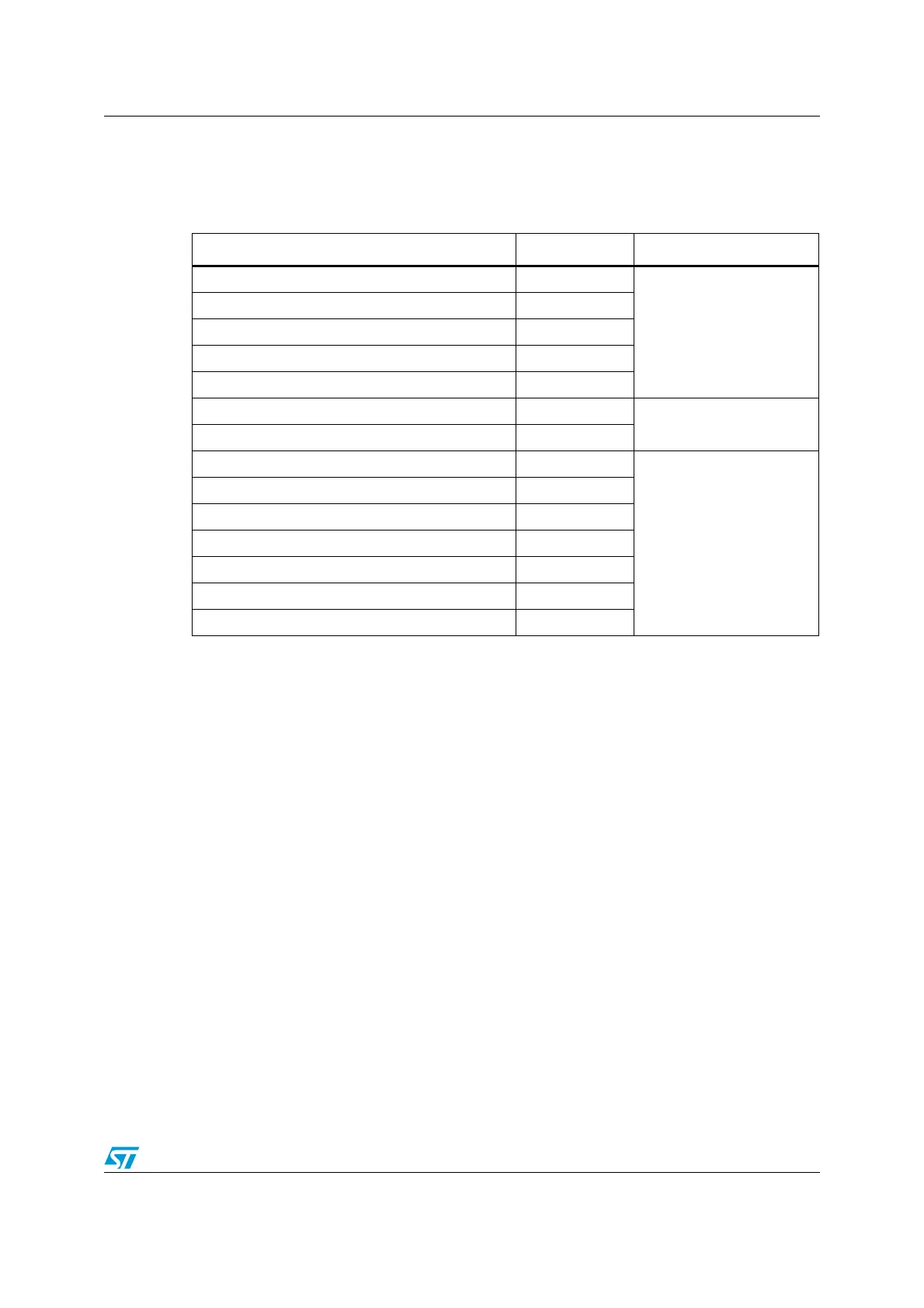

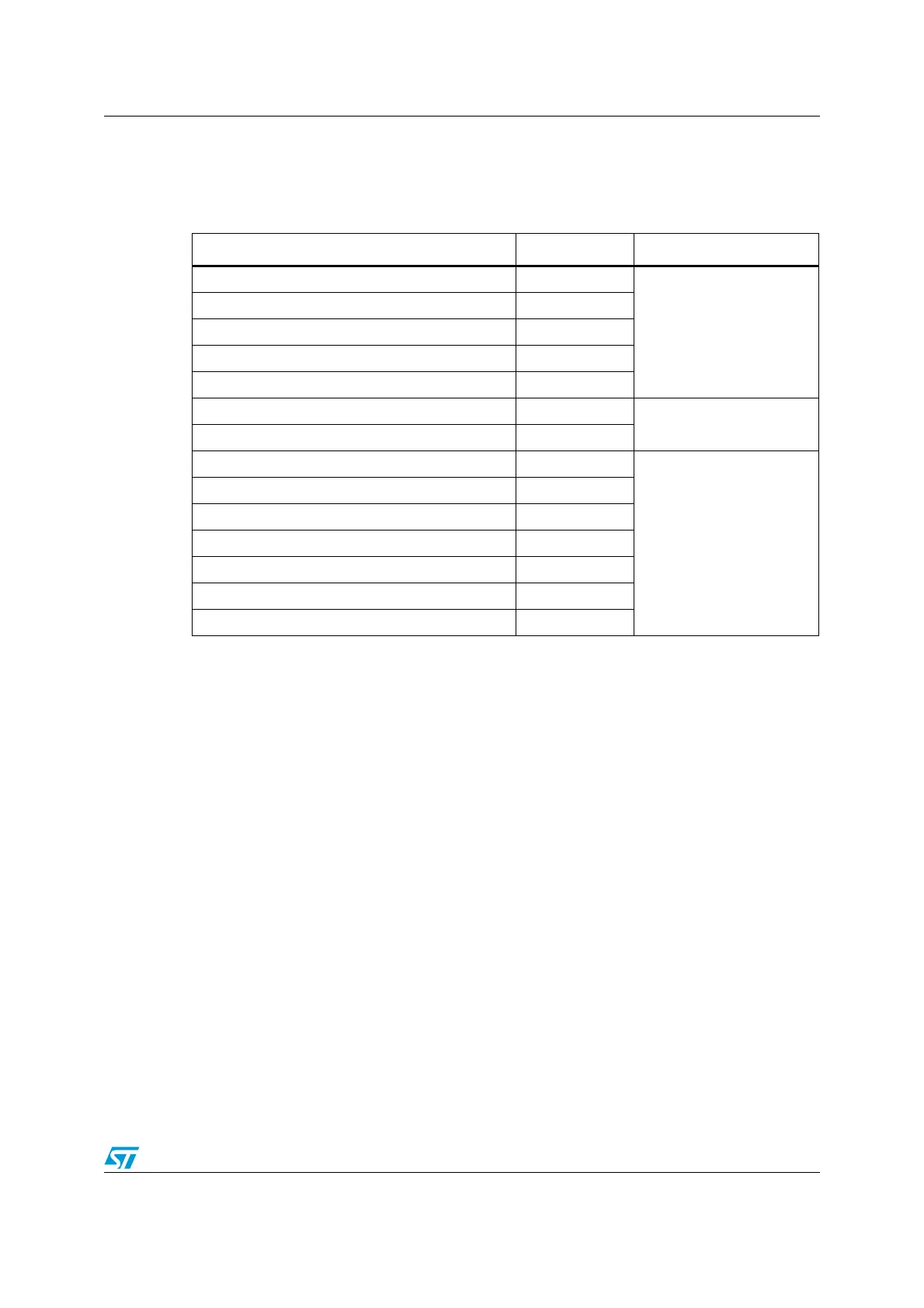

Table 105. I

2

C Interrupt requests

Interrupt event Event flag Enable control bit

Start bit sent (Master) SB

ITEVFEN

Address sent (Master) or Address matched (Slave) ADDR

10-bit header sent (Master) ADD10

Stop received (Slave) STOPF

Data byte transfer finished BTF

Receive buffer not empty RxNE

ITEVFEN and ITBUFEN

Transmit buffer empty TxE

Bus error BERR

ITERREN

Arbitration loss (Master) ARLO

Acknowledge failure AF

Overrun/Underrun OVR

PEC error PECERR

Timeout/Tlow error TIMEOUT

SMBus Alert SMBALERT

Loading...

Loading...