Digital camera interface (DCMI) RM0090

347/1422 Doc ID 018909 Rev 4

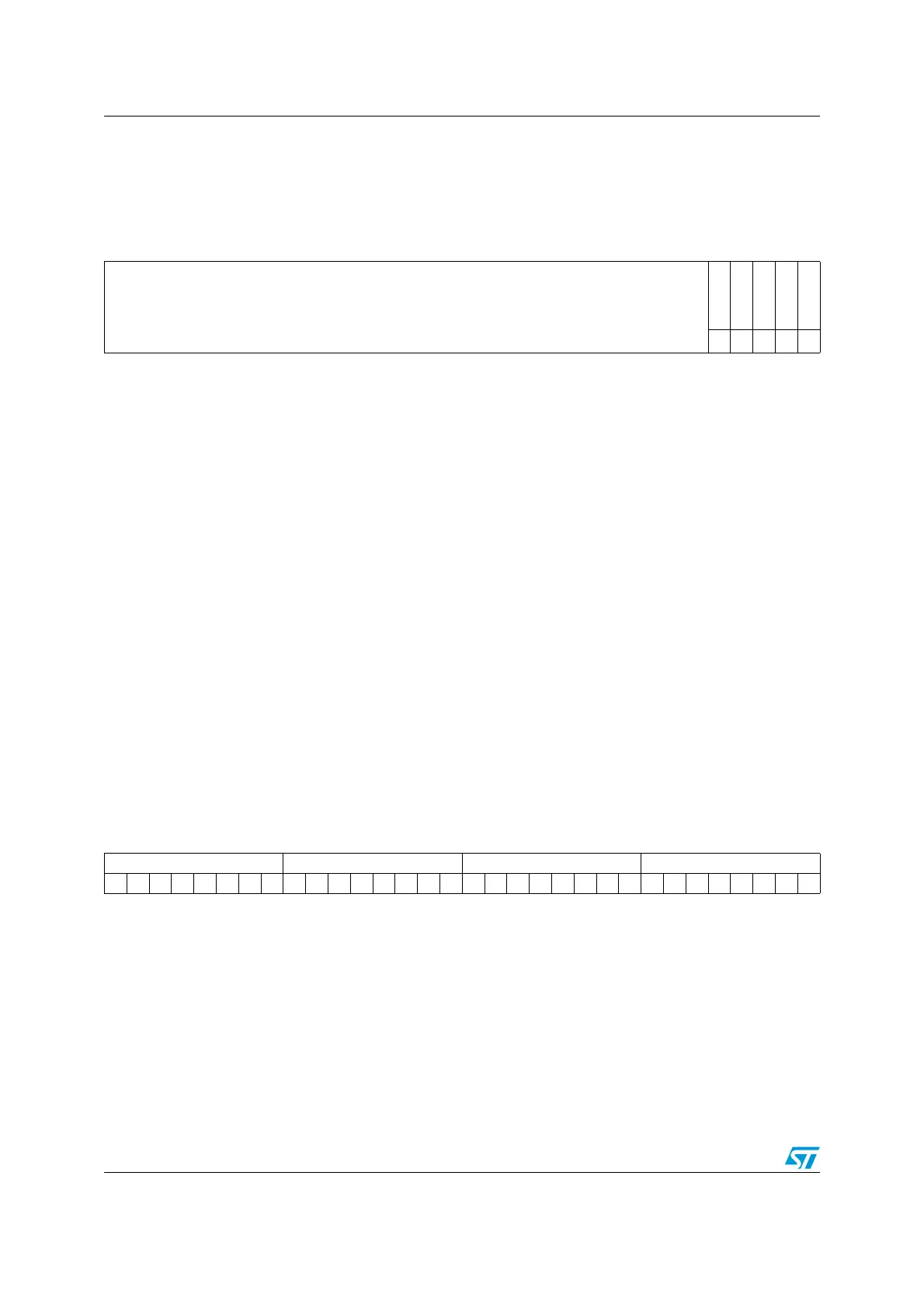

13.8.6 DCMI interrupt clear register (DCMI_ICR)

Address offset: 0x14

Reset value: 0x0000 0x0000

The DCMI_ICR register is write-only. Writing a ‘1’ into a bit of this register clears the

corresponding bit in the DCMI_RIS and DCMI_MIS registers. Writing a ‘0’ has no effect.

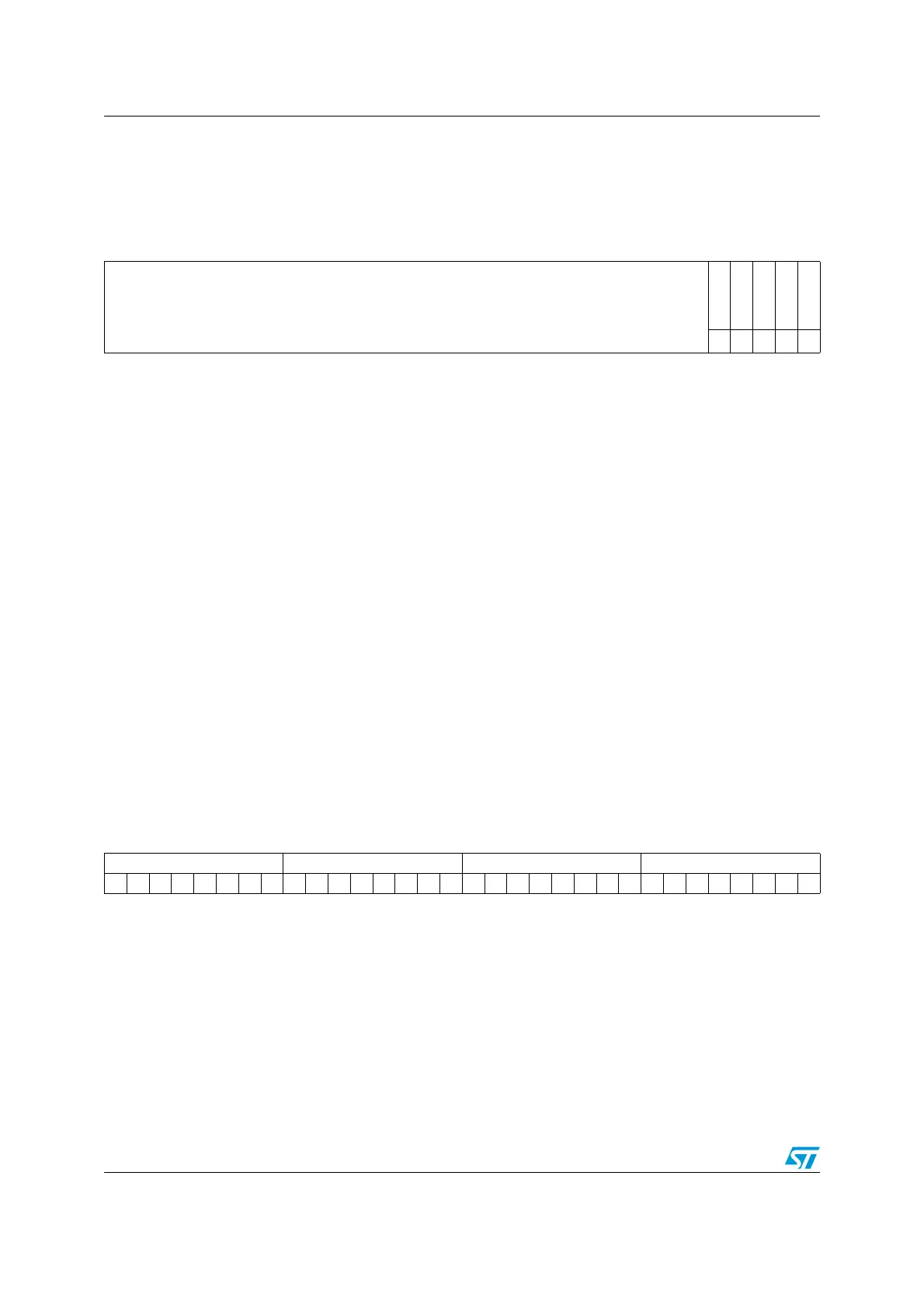

13.8.7 DCMI embedded synchronization code register (DCMI_ESCR)

Address offset: 0x18

Reset value: 0x0000 0x0000

313029282726252423222120191817161514131211109876543210

Reserved

LINE_ISC

VSYNC_ISC

ERR_ISC

OVR_ISC

FRAME_ISC

wwwww

Bit 15:5 Reserved, must be kept at reset value.

Bit 4 LINE_ISC: line interrupt status clear

Writing a ‘1’ into this bit clears LINE_RIS in the DCMI_RIS register

Bit 3 VSYNC_ISC: Vertical synch interrupt status clear

Writing a ‘1’ into this bit clears the VSYNC_RIS bit in DCMI_RIS

Bit 2 ERR_ISC: Synchronization error interrupt status clear

Writing a ‘1’ into this bit clears the ERR_RIS bit in DCMI_RIS

Note: This bit is available only in embedded synchronization mode.

Bit 1 OVR_ISC: Overrun interrupt status clear

Writing a ‘1’ into this bit clears the OVR_RIS bit in DCMI_RIS

Bits 0 FRAME_ISC: Capture complete interrupt status clear

Writing a ‘1’ into this bit clears the FRAME_RIS bit in DCMI_RIS

313029282726252423222120191817161514131211109876543210

FEC LEC LSC FSC

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...