RM0090 Serial peripheral interface (SPI)

Doc ID 018909 Rev 4 824/1422

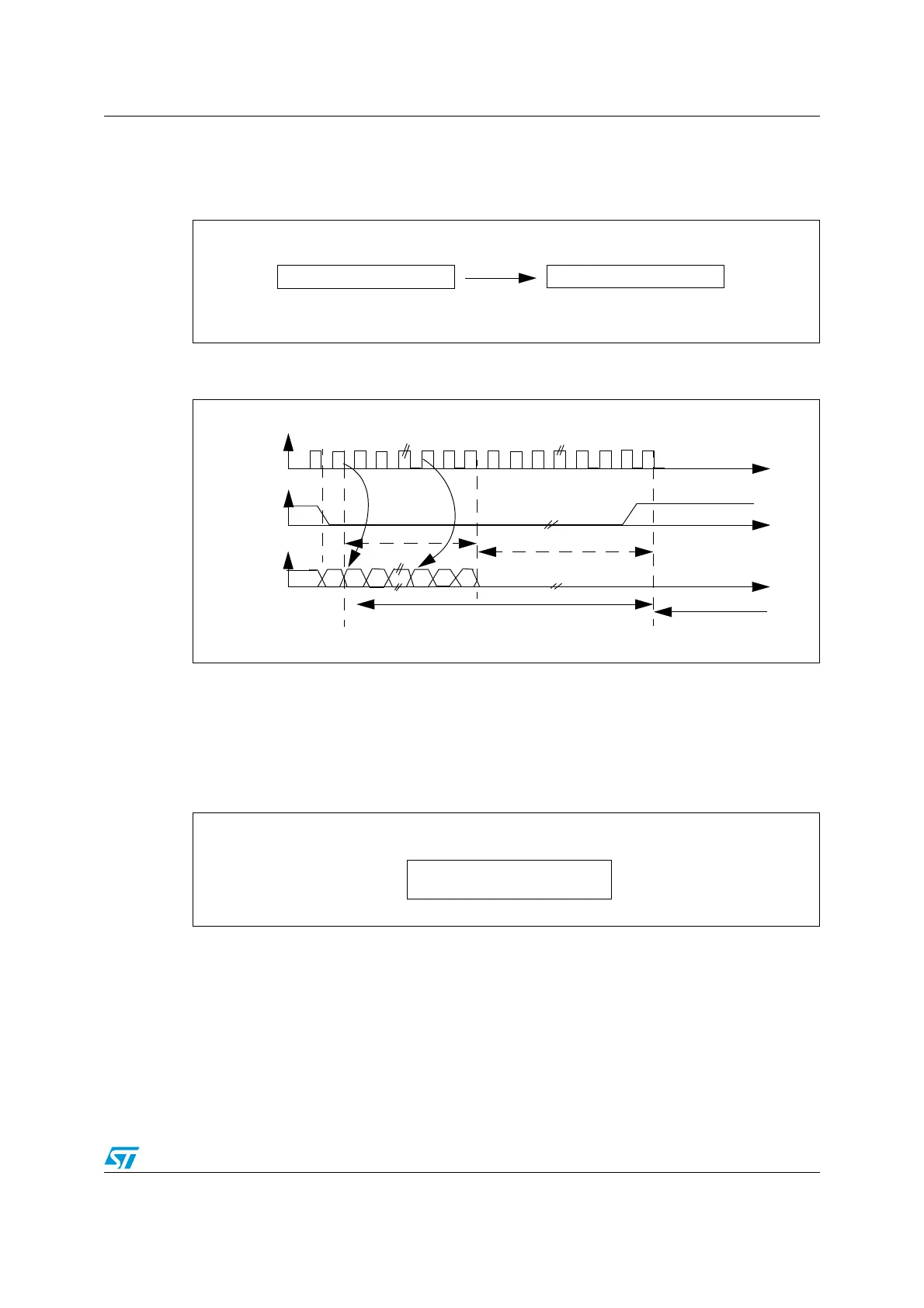

● In reception mode:

if data 0x8EAA33 is received:

Figure 292. Receiving 0x8EAA33

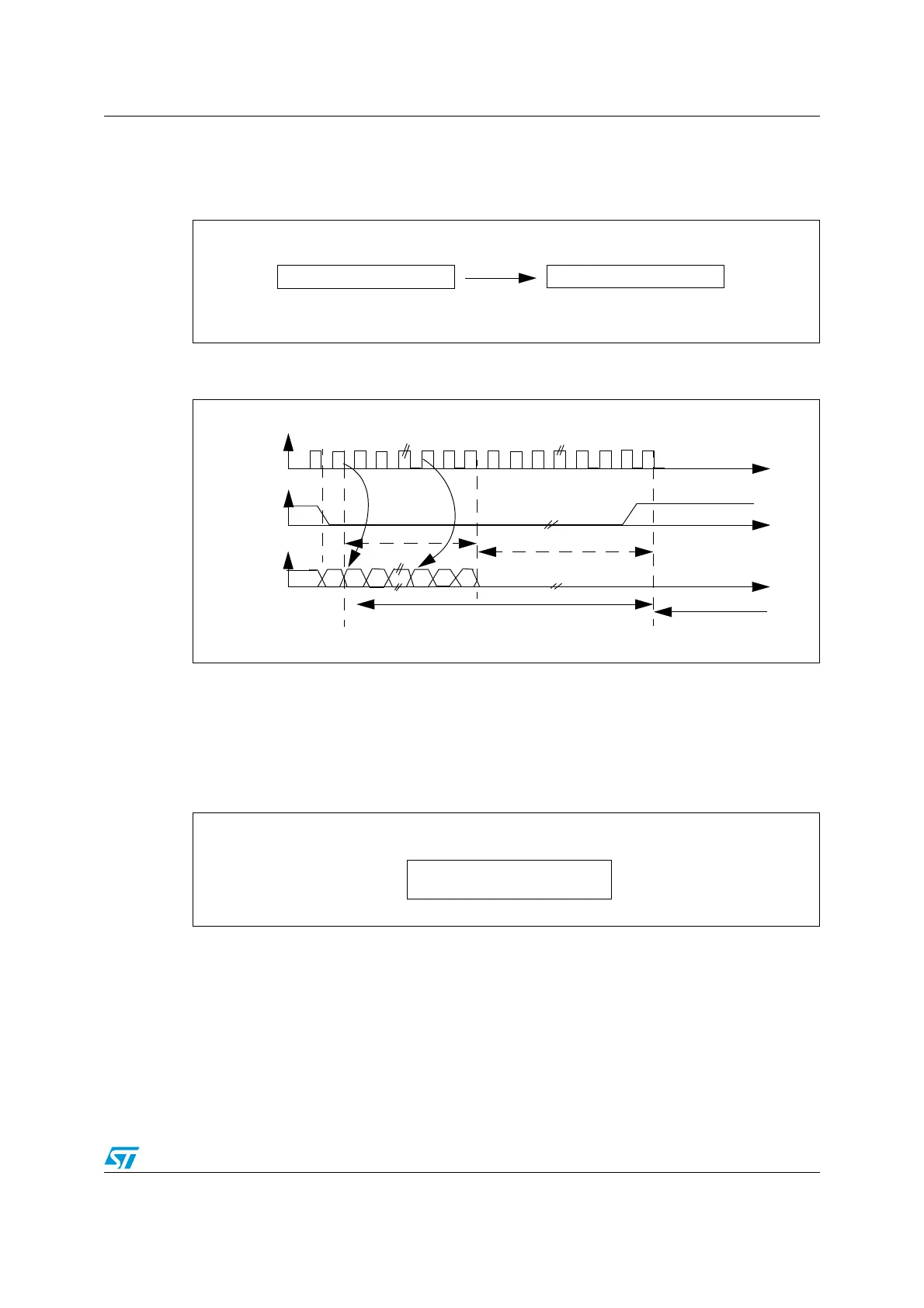

Figure 293. I

2

S Philips standard (16-bit extended to 32-bit packet frame with

CPOL = 0)

When 16-bit data frame extended to 32-bit channel frame is selected during the I

2

S

configuration phase, only one access to SPI_DR is required. The 16 remaining bits are

forced by hardware to 0x0000 to extend the data to 32-bit format.

If the data to transmit or the received data are 0x76A3 (0x76A30000 extended to 32-bit), the

operation shown in Figure 294 is required.

Figure 294. Example

For transmission, each time an MSB is written to SPI_DR, the TXE flag is set and its

interrupt, if allowed, is generated to load SPI_DR with the new value to send. This takes

place even if 0x0000 have not yet been sent because it is done by hardware.

For reception, the RXNE flag is set and its interrupt, if allowed, is generated when the first

16 MSB half-word is received.

In this way, more time is provided between two write or read operations, which prevents

underrun or overrun conditions (depending on the direction of the data transfer).

0x8EAA 0x3300

Only the 8MSB are right

First read from Data register

Second read from Data register

The 8 LSB will always be 00

CK

WS

SD

Channel left 32-bit

Channel right

MSB

LSB

16-bit remaining

16-bit data

0 forced

Transmission Reception

0X76A3

Only one access to SPI_DR

Loading...

Loading...