Cryptographic processor (CRYP) RM0090

585/1422 Doc ID 018909 Rev 4

20.6.8 CRYP raw interrupt status register (CRYP_RISR)

Address offset: 0x18

Reset value: 0x0000 0001

The CRYP_RISR register is the raw interrupt status register. It is a read-only register. On a

read, this register gives the current raw status of the corresponding interrupt prior to

masking. A write has no effect.

20.6.9 CRYP masked interrupt status register (CRYP_MISR)

Address offset: 0x1C

Reset value: 0x0000 0000

The CRYP_MISR register is the masked interrupt status register. It is a read-only register.

On a read, this register gives the current masked status of the corresponding interrupt prior

to masking. A write has no effect.

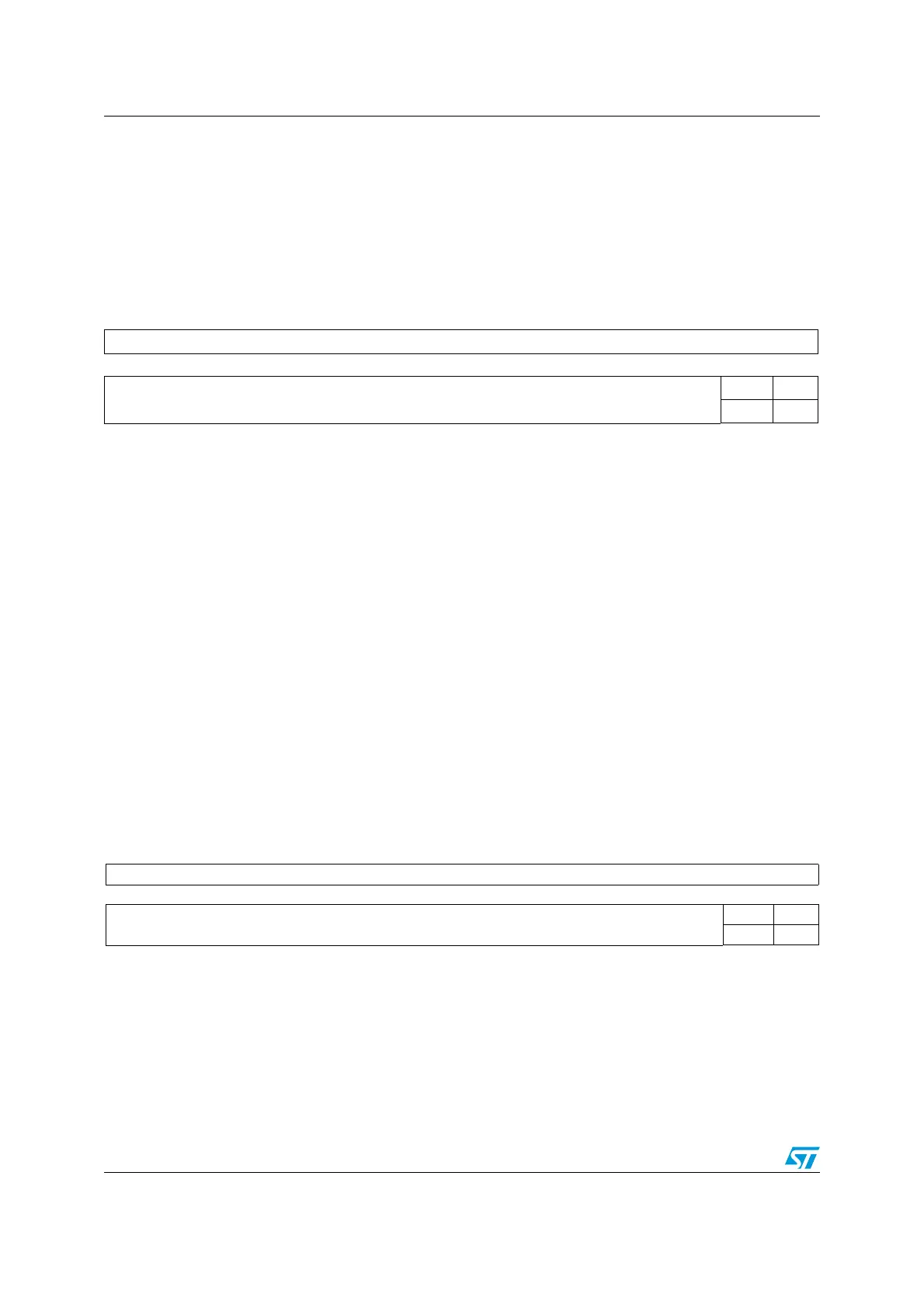

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15141312111098765432 1 0

Reserved

OUTRIS INRIS

rr

Bit 31:2 Reserved, must be kept at reset value

Bit 1 OUTRIS: Output FIFO service raw interrupt status

Gives the raw interrupt state prior to masking of the output FIFO service

interrupt.

0: Raw interrupt not pending

1: Raw interrupt pending

Bit 0 INRIS: Input FIFO service raw interrupt status

Gives the raw interrupt state prior to masking of the Input FIFO service interrupt.

0: Raw interrupt not pending

1: Raw interrupt pending

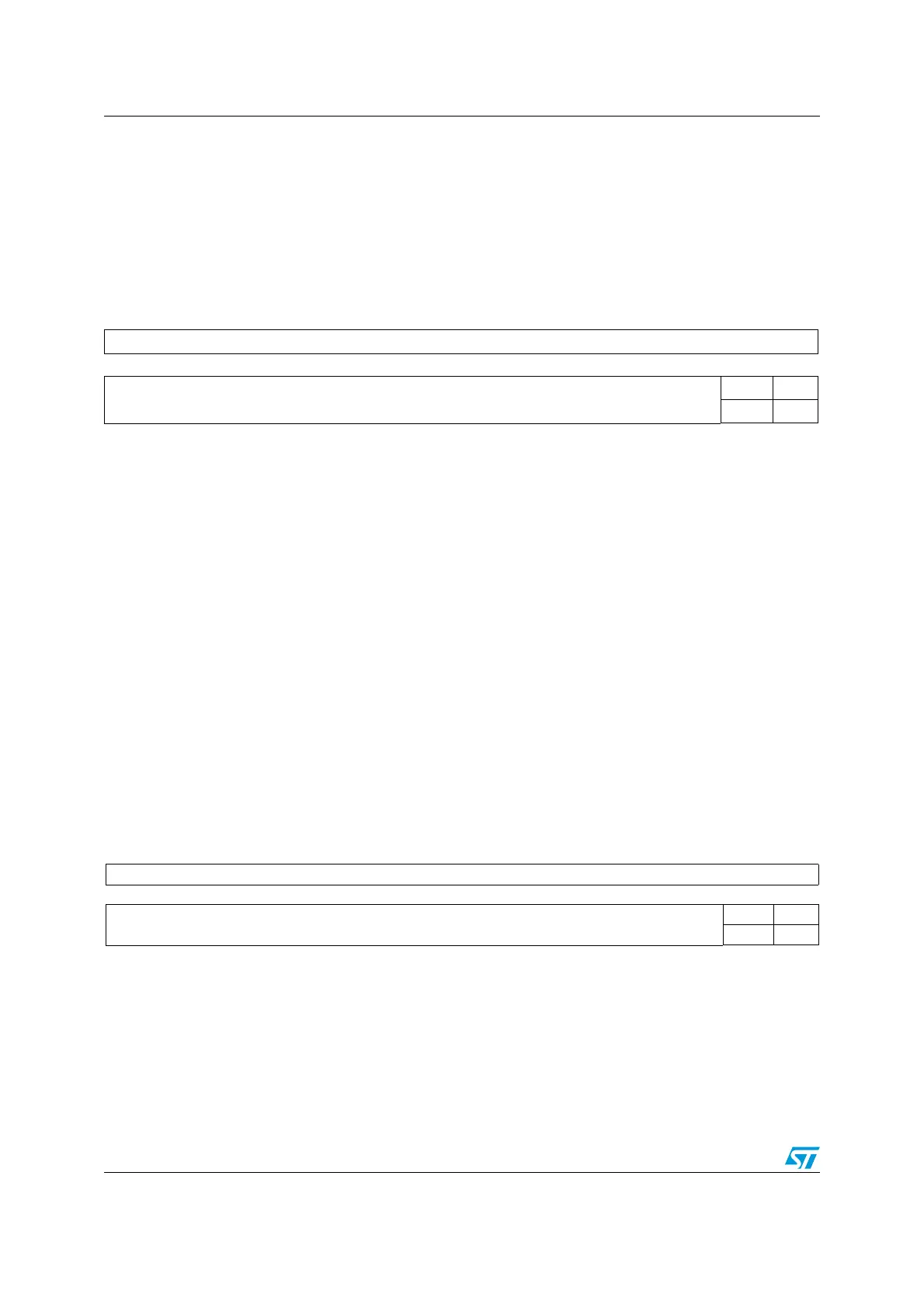

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

OUTMIS INMIS

rr

Bit 31:2 Reserved, must be kept at reset value

Bit 1 OUTMIS: Output FIFO service masked interrupt status

Gives the interrupt state after masking of the output FIFO service interrupt.

0: Interrupt not pending

1: Interrupt pending

Loading...

Loading...