RM0090 Digital-to-analog converter (DAC)

Doc ID 018909 Rev 4 324/1422

12.5.2 DAC software trigger register (DAC_SWTRIGR)

Address offset: 0x04

Reset value: 0x0000 0000

12.5.3 DAC channel1 12-bit right-aligned data holding register

(DAC_DHR12R1)

Address offset: 0x08

Reset value: 0x0000 0000

Bit 1 BOFF1: DAC channel1 output buffer disable

This bit is set and cleared by software to enable/disable DAC channel1 output buffer.

0: DAC channel1 output buffer enabled

1: DAC channel1 output buffer disabled

Bit 0 EN1: DAC channel1 enable

This bit is set and cleared by software to enable/disable DAC channel1.

0: DAC channel1 disabled

1: DAC channel1 enabled

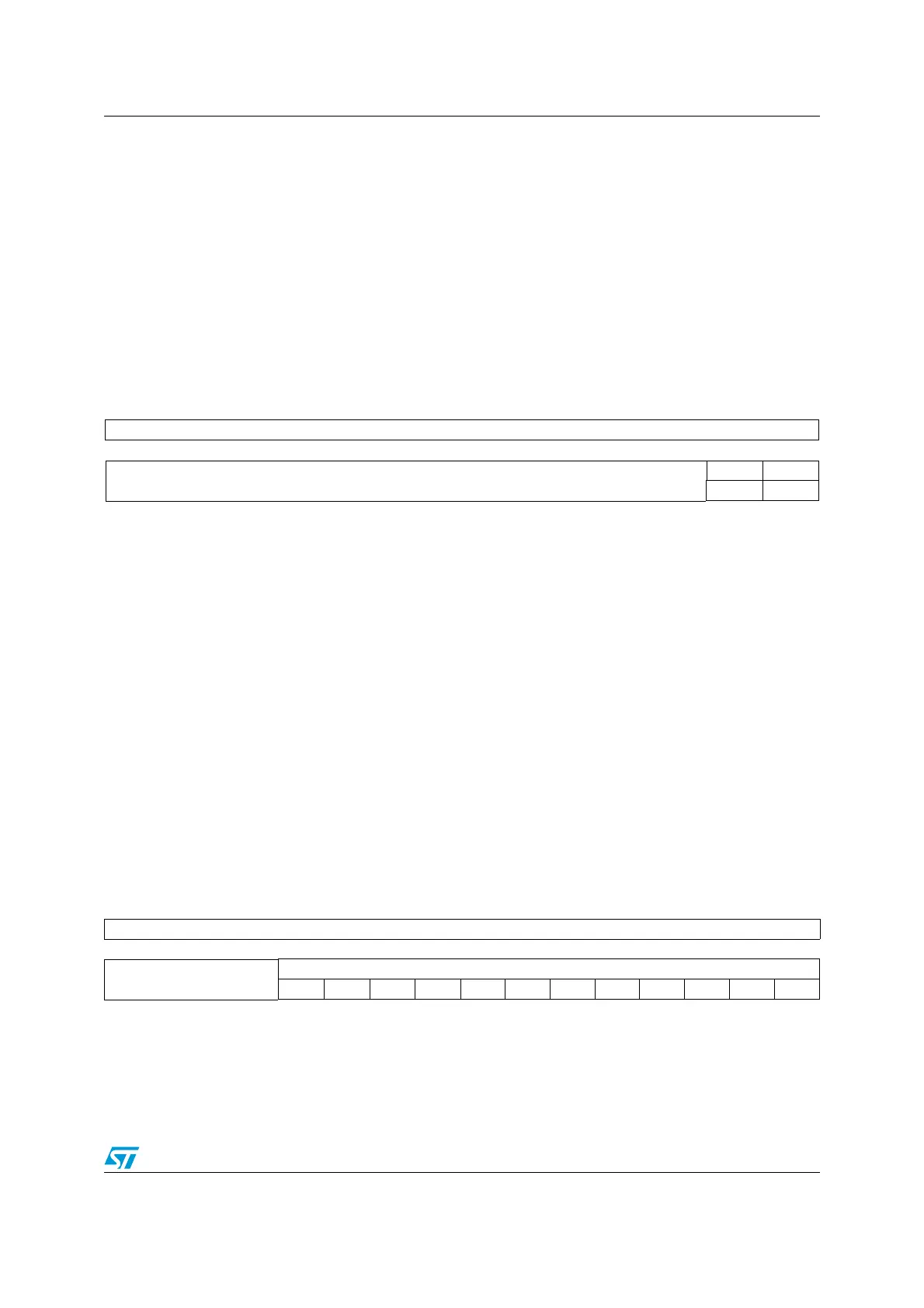

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

SWTRIG2 SWTRIG1

ww

Bits 31:2 Reserved, must be kept at reset value.

Bit 1 SWTRIG2: DAC channel2 software trigger

This bit is set and cleared by software to enable/disable the software trigger.

0: Software trigger disabled

1: Software trigger enabled

Note: This bit is cleared by hardware (one APB1 clock cycle later) once the DAC_DHR2

register value has been loaded into the DAC_DOR2 register.

Bit 0 SWTRIG1: DAC channel1 software trigger

This bit is set and cleared by software to enable/disable the software trigger.

0: Software trigger disabled

1: Software trigger enabled

Note: This bit is cleared by hardware (one APB1 clock cycle later) once the DAC_DHR1

register value has been loaded into the DAC_DOR1 register.

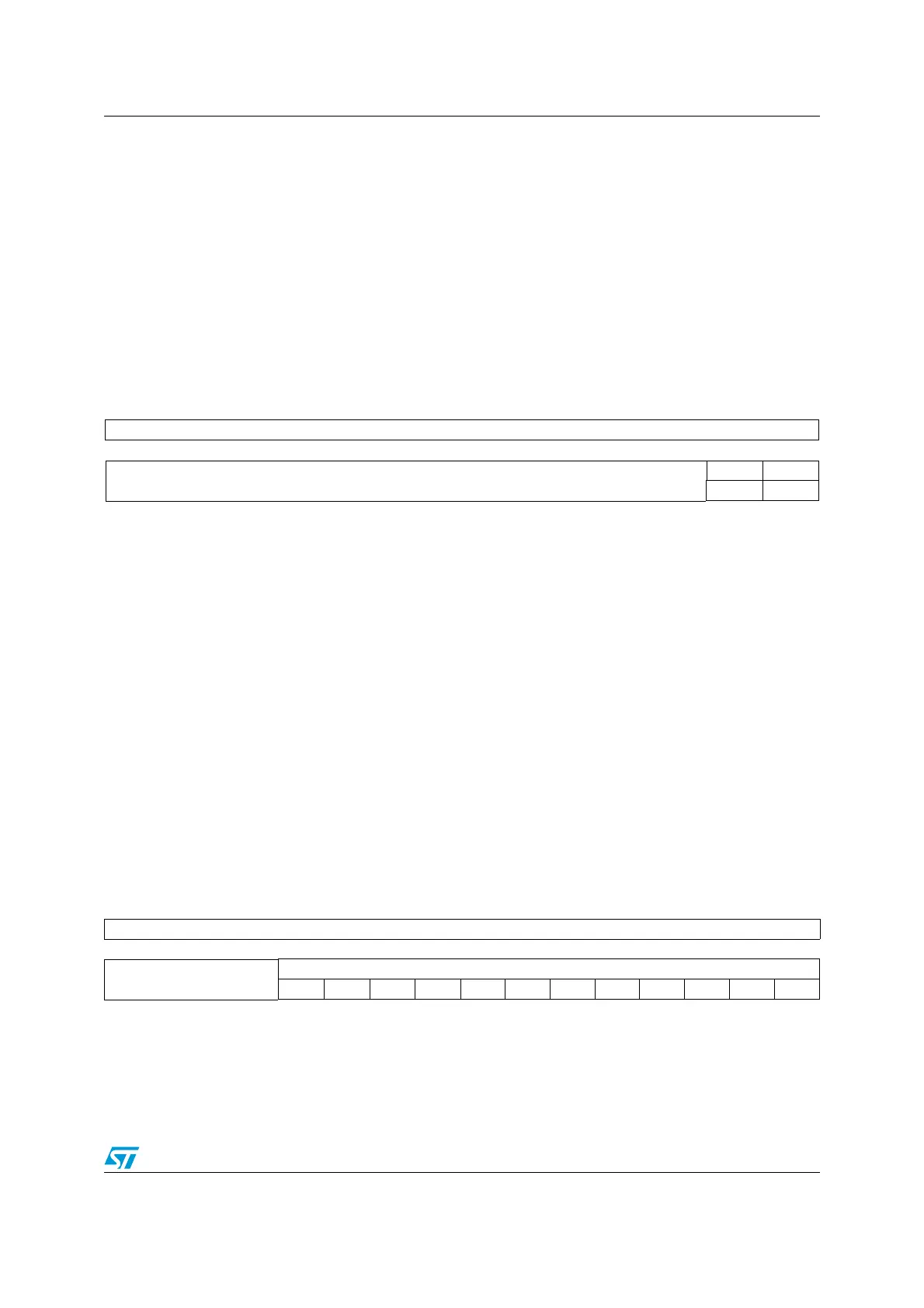

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

DACC1DHR[11:0]

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:12 Reserved, must be kept at reset value.

Bit 11:0 DACC1DHR[11:0]: DAC channel1 12-bit right-aligned data

These bits are written by software which specifies 12-bit data for DAC channel1.

Loading...

Loading...