RM0090 Cryptographic processor (CRYP)

Doc ID 018909 Rev 4 548/1422

20 Cryptographic processor (CRYP)

This section applies to the whole STM32F4xx family devices, unless otherwise specified.

20.1 CRYP introduction

The cryptographic processor can be used to both encipher and decipher data using the

DES, Triple-DES or AES (128, 192, or 256) algorithms. It is a fully compliant implementation

of the following standards:

● The data encryption standard (DES) and Triple-DES (TDES) as defined by Federal

Information Processing Standards Publication (FIPS PUB 46-3, 1999 October 25). It

follows the American National Standards Institute (ANSI) X9.52 standard.

● The advanced encryption standard (AES) as defined by Federal Information

Processing Standards Publication (FIPS PUB 197, 2001 November 26)

The CRYP processor performs data encryption and decryption using DES and TDES

algorithms in Electronic codebook (ECB) or Cipher block chaining (CBC) mode.

The CRYP peripheral is a 32-bit AHB2 peripheral. It supports DMA transfer for incoming and

processed data, and has input and output FIFOs (each 8 words deep).

20.2 CRYP main features

● Suitable for AES, DES and TDES enciphering and deciphering operations

● AES

– Supports the ECB, CBC, CTR, CCM and GCM chaining algorithms (CCM and

GCM are available on STM32F42xxx and STM32F43xxx only)

– Supports 128-, 192- and 256-bit keys

– 4 × 32-bit initialization vectors (IV) used in the CBC, CTR, CCM and GCM modes

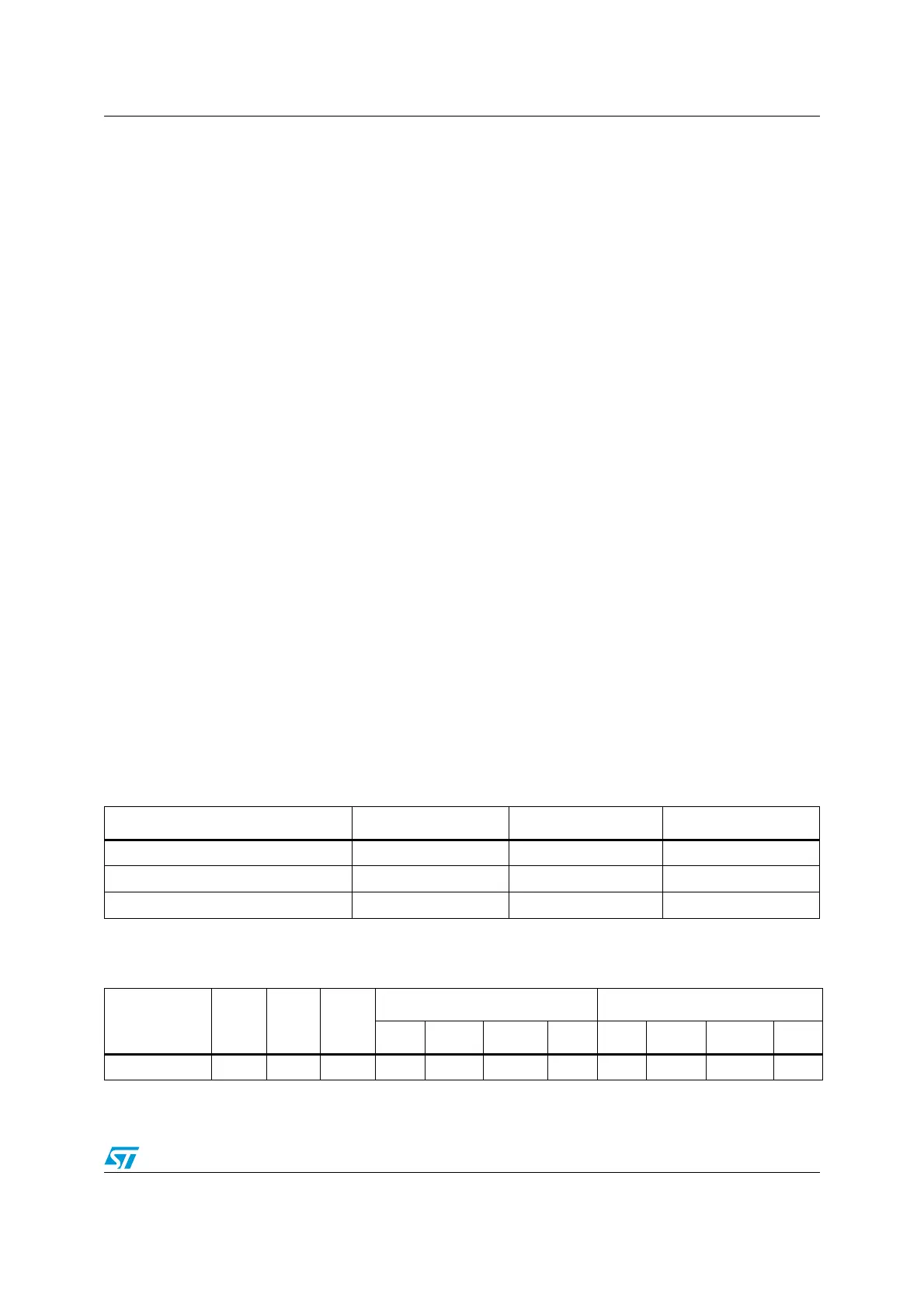

Table 89. Number of cycles required to process each 128-bit block

(STM32F405xx/07xx and STM32F415xx/17xx)

Algorithm / Key size ECB CBC CTR

128b 14 14 14

192b 16 16 16

256b 18 18 18

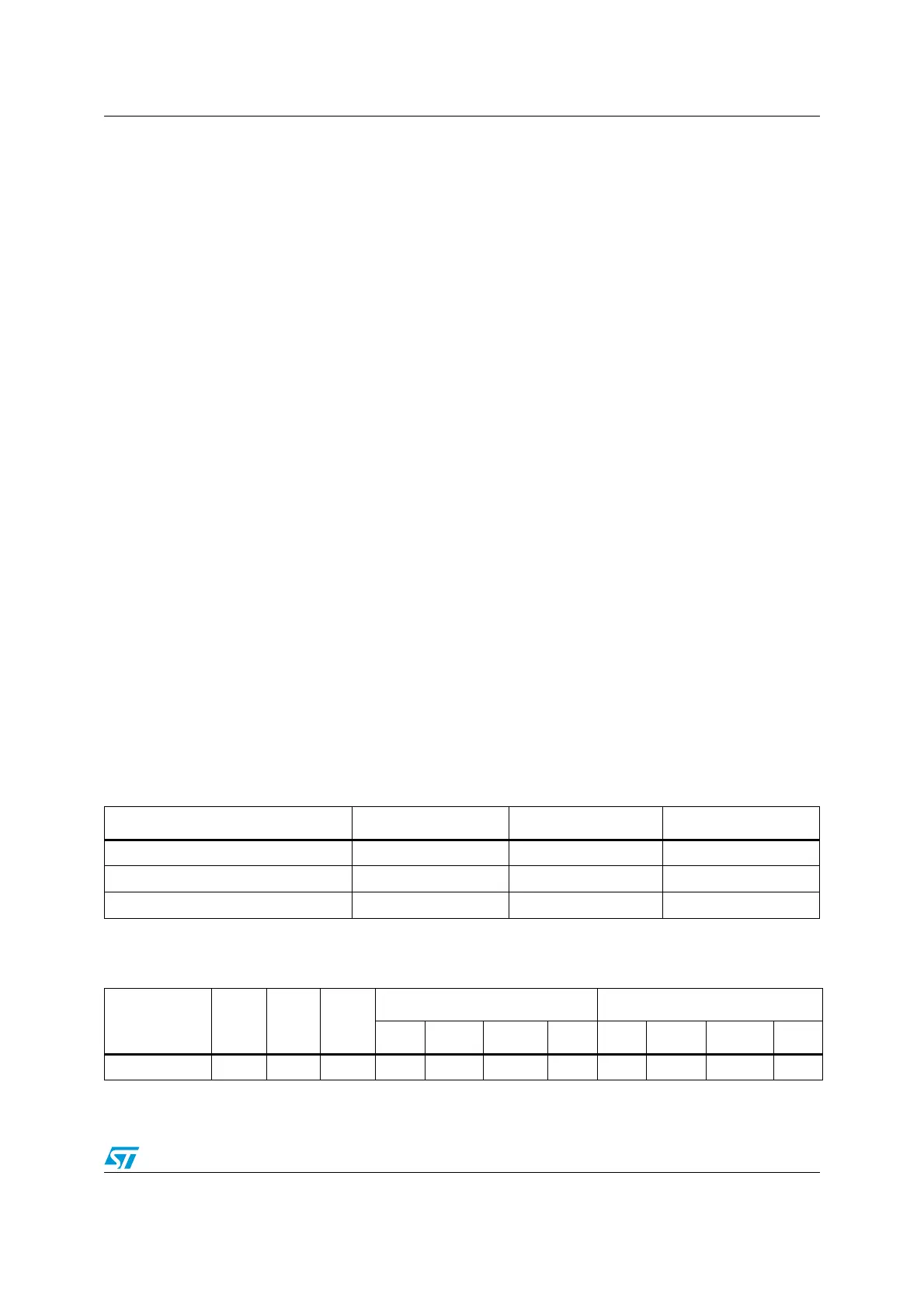

Table 90. Number of cycles required to process each 128-bit block

(STM32F42xxx and STM32F43xxx)

Algorithm /

Key size

ECB CBC CTR

GCM CCM

Init Header Payload Tag Init Header Payload Tag

128b 14 14 14 24 10 14 14 12 14 25 14

Loading...

Loading...